VME64 Bus Adapters: 800 VME64 to VME64, 810 VME64 to PCI, 820 VME64 to PMC, 830 VME64 to CompactPCI

Hardware Manual

# Disclaimer

Please read and abide by the following paragraphs. Questions and comments should be directed to:

Technical Publications Department SBS Technologies, Inc. 1284 Corporate Center Drive St. Paul, MN 55121-1245 651-905-4700

SBS Technologies does not authorize the use of its components in life support applications where failure or malfunction of the component may result in injury or death. In accordance with SBS' terms and conditions of sale, the user of SBS components in any and all life support applications assumes all risks arising out of such use and further agrees to indemnify and hold SBS harmless against any and all claims of whatsoever kind or nature (including claims of culpable conduct [strict liability, negligence or breach of warranty] on the part of SBS) for all costs of defending any such claims.

SBS does not authorize the use of its components in control and process applications where failure or malfunction of the component may result in radioactive releases, explosions, environmental damage/contamination, personal injury or death. In accordance with SBS' terms and conditions of sale, the user of SBS components in any and all control and process applications assumes all risks arising out of such use and further agrees to indemnify and hold SBS harmless against any and all claims of whatsoever kind or nature (including claims of culpable conduct [strict liability, negligence or breach of warranty] on the part of SBS) for all costs of defending any such claims.

SBS makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. SBS assumes no responsibility for any errors that may appear in this document. The information in this document is subject to change without notice.

#### U.S. GOVERNMENT LIMITED RIGHTS

This documentation is provided with limited rights. Use, duplication or disclosure by the Government is subject to the restrictions as set forth in subdivision (b) (3) (iii) of the Rights in Technical Data and Computer Software Clause of DFAR252.227-7013 (October 1988) and in similar clauses in the FAR and NASA FAR Supplement. Manufacturer is SBS Technologies, Inc., 1284 Corporate Center Drive, St. Paul, MN 55121-1245.

Copyright  $^{\circ}$  2004 by SBS Technologies, Inc. Portions reprinted with permission of the PCI Special Interest Group.

Revision 1.0 20040329 Pub. No. 85913163

# **Preface**

This manual describes SBS VME64 bus adapters that connect two computer systems via fiber-optic cable. Adapter Models included are:

| Model | Bus Connectivity    |

|-------|---------------------|

| 800   | VME64 to VME64      |

| 810   | VME64 to PCI        |

| 820   | VME64 to PMC        |

| 830   | VME64 to CompactPCI |

The manual includes information about the adapters' operation, installation, configuration, and control registers.

In this manual all references to "the 8xx" refer to all for adapters. If any text refers to just one of the models, that model will be identified by "800 only", "810 only", "820 only", or "830 only". PCI is used to refer to the three PCI formats: PCI, PMC, and CompactPCI.

To simplify installation and eliminate operation problems, SBS recommends that you review this manual before beginning to install your new adapter cards. Please pay close attention to the sections on card configuration and adapter registers.

- Chapter 1 provides an overview of the adapter, product description, specifications and requirements, and supporting products.

- Chapter 2 gets you started with information about unpacking the adapter package, adapter installation, Help, and additional references.

- Chapter 3 discusses basic bus issues, features common to both adapter cards, and cable conflict issues.

- Chapter 4 provides a broad overview of the PCI adapter card, including how the major features fit together and how they are used. This chapter also introduces the various memory windows.

- Chapter 5 talks about how to use PCI adapter card functions, including making VME64 accesses, allowing VME64 accesses, handling interrupts, initiating a DMA operation from PCI, and configuration registers.

- Chapter 6 describes Control and Status Registers (CSR) accessed from the PCI bus.

- Chapter 7 is an overview of the VME64 adapter card.

- Chapter 8 deals with using the VME64 adapter card functions, such as: making accesses to PCI, allowing PCI accesses, handling interrupts, and initiating a DMA operation from VME64 bus.

- Chapter 9 describes Control and Status Registers (CSR) accessed from the VMEbus.

- Chapter 10 contains details for setting jumpers on the VME64 adapter card.

- Chapter 11 provides suggestions and solutions for common problems with setting up and using the adapter.

- Appendix A is a glossary of terms used throughout this manual.

■ Appendix B provides information about VME64 addressing, including pin assignments and address modifiers.

# Important Notes:

- Make sure you follow proper ESD handling procedures (refer to EIA-625, ESD Association Handbook, or MIL-HDBK-263) when working with cards and components.

- Be sure power is OFF before installing adapter cards.

- Please read this manual thoroughly before trying to install or use the adapter.

# **Table Of Contents**

| Chapter | 1:  | Introduction                                                            | 11 |

|---------|-----|-------------------------------------------------------------------------|----|

|         |     | Overview                                                                |    |

|         | 1.1 | Adapter Features                                                        | 12 |

|         | 1.2 | Supporting Products                                                     |    |

|         |     | 1.2.1 Cables                                                            |    |

|         | 1 0 | 1.2.2 Dual Port RAM                                                     |    |

|         |     | System Controller Operation                                             |    |

|         |     | Adapter Control And Status Registers (CSRs)  Direct Memory Access (DMA) |    |

|         |     | Interrupts                                                              |    |

|         |     | Mapping Registers                                                       |    |

| Chapter |     | Getting Started                                                         |    |

| Onaptor |     | -                                                                       |    |

|         |     | Unpacking                                                               |    |

|         |     | Help!                                                                   |    |

|         | 2.2 | 2.2.1 Configure The Adapter Cards                                       |    |

|         |     | 2.2.2 Installing The PCI Adapter Card                                   |    |

|         |     | 2.2.3 Installing The VME64 Adapter Card                                 |    |

|         |     | 2.2.4 Connecting The Adapter Cable                                      | 19 |

|         | 2.3 | Additional References                                                   |    |

| Chapter | 3:  | VME64 to PCI Adapters                                                   | 21 |

|         | 3.0 | Introduction                                                            | 21 |

|         |     | PCI Bus                                                                 |    |

|         |     | VMEbus                                                                  |    |

|         |     | 3.2.1 System Controller Operation                                       | 21 |

|         |     | 3.2.2 Backplane Jumpers                                                 |    |

|         |     | 3.2.3 VMEbus Address Modifiers                                          |    |

|         |     | 3.2.4 VMEbus Interrupts And The IACK Cycle                              | 24 |

|         | 3.3 | Bridging PCI And VMEbus                                                 |    |

|         |     | 3.3.1 Programmed Interrupt To Transmitter (PT)                          |    |

|         |     | 3.3.2 Programmed Interrupt To Receiver (PR)                             |    |

|         |     | 3.3.3 Direct Memory Access (DMA)                                        |    |

|         | 3 4 | Accessing Windows                                                       |    |

|         |     | Byte And Word Swapping                                                  |    |

|         |     | 3.5.1 Data Accesses                                                     |    |

|         |     | 3.5.2 Little Endian Versus Big Endian                                   |    |

|         |     | 3.5.3 Swapping For Byte Accesses                                        |    |

|         |     | 3.5.4 Swapping For Word Accesses                                        |    |

|         |     | 3.5.5 Longword Accesses                                                 | 32 |

|         | o . | 3.5.6 Access Width Versus Data Width                                    |    |

|         | 3.6 | Loopback                                                                | 33 |

| Chapter | 4:  | The PCI Adapter Card                                                    | 35 |

|         | 4.0 | Introduction                                                            | 35 |

|            | Configuration Registers                                           |    |

|------------|-------------------------------------------------------------------|----|

|            | PCI CSR                                                           |    |

|            | Mapping Registers                                                 |    |

|            | Remote Memory Window                                              |    |

|            | PCI Adapter Card LEDs                                             |    |

| Chapter 5: | Using PCI Adapter Card Functions                                  | 39 |

| 5.0        | Introduction                                                      | 39 |

| 5.1        | Finding And Mapping the Adapter                                   | 39 |

| 5.2        | Initialization                                                    | 39 |

| 5.3        | Accessing Remote Memory                                           | 40 |

|            | 5.3.1 VMEbus Memory                                               | 40 |

|            | 5.3.2 Dual Port RAM                                               | 40 |

|            | 5.3.3 Mapping Register Window                                     | 41 |

|            | 5.3.3.1 Remote Memory Mapping Register Format                     |    |

|            | 5.3.4 PCI To VMEbus Address                                       | 42 |

|            | 5.3.5 Example of Accessing VMEbus                                 |    |

| 5.4        | Allowing VMEbus Accesses                                          |    |

|            | 5.4.1 Setting Up PCI Memory                                       |    |

|            | 5.4.2 VMEbus Remote RAM Window                                    |    |

|            | 5.4.3 Mapping Register Window                                     |    |

|            | 5.4.3.1 VMEbus-To-PCI Bus Mapping Register Format                 |    |

|            | 5.4.4 Example: Allowing VMEbus Accesses                           |    |

| 5.5        | Handling Interrupts                                               |    |

|            | 5.5.1 Programmed Interrupts                                       |    |

|            | 5.5.1.1 Sending PT Interrupts                                     |    |

|            | 5.5.1.2 Receiving PT Interrupts                                   |    |

|            | 5.5.1.3 Sending PR Interrupts                                     |    |

|            | 5.5.1.4 Receiving PR Interrupts                                   |    |

|            | 5.5.2 Error Interrupts                                            |    |

|            | 5.5.3 VMEbus Backplane Interrupts                                 |    |

|            | 5.5.4 DMA Interrupts                                              |    |

| Г /        | 5.5.5 Writing An Interrupt Service Routine                        |    |

| 5.6        | Initiating A DMA Operation                                        |    |

|            | 5.6.1 Mapping Register Window                                     |    |

|            | 5.6.1.1 DMA-To-PCI Bus Mapping Register Format                    |    |

|            | 5.6.3 Other CSRs                                                  |    |

|            | 5.6.4 DMA Transfer Modes                                          |    |

|            | 5.6.5 When Is The DMA Operation Done?                             |    |

|            | 5.6.5.1 DMA Done Interrupt                                        |    |

|            | 5.6.5.2 Polling For DMA Done Bit                                  |    |

|            | 5.6.6 Programming Sequence For Initiating A DMA Transfer From PCI |    |

|            | 5.6.7 Things To Remember                                          |    |

|            | 5.6.8 Example Of Initiating A DMA Operation                       |    |

| 5.7        | Configuration Registers                                           |    |

| 5.7        | 5.7.1 Finding And Identifying The PCI Adapter Card                |    |

|            | 5.7.1.1 Vendor ID Register                                        |    |

|            | 5.7.1.2 Device ID Register                                        |    |

|            | 5.7.1.3 Revision ID Register                                      |    |

|            | 5.7.1.4 Class Code Register                                       |    |

|            | J                                                                 |    |

|         | 5.7.2        | Where Are The Windows?                                              |          |

|---------|--------------|---------------------------------------------------------------------|----------|

|         |              | 5.7.2.2 Memory Mapped Node I/O Base Address Register                |          |

|         |              | 5.7.2.3 Mapping Register Base Address Register                      |          |

|         |              | 5.7.2.4 Remote Memory Base Address Register                         |          |

|         | 5.7.3        | Other Registers                                                     |          |

|         |              | 5.7.3.1 Command Register                                            |          |

|         |              | 5.7.3.2 Status Register                                             |          |

|         |              | 5.7.3.3 Interrupt Line Register                                     |          |

|         |              | 5.7.3.4 Latency Timer Register                                      | 67       |

| Chapter | 6: CSR Acces | ssed From The PCI Bus                                               | 69       |

|         | 6.0 CSR Acce | essed From The PCI Bus                                              | 69       |

|         |              | de Registers                                                        |          |

|         |              | Local Command Register                                              |          |

|         |              | Interrupt Control Register                                          |          |

|         |              | Local Status Register                                               |          |

|         | 6.1.4        | Interrupt Status Register                                           | 73       |

|         | 6.1.5        | PCI Control Register                                                | 73       |

|         |              | PCI Loopback Control Register                                       |          |

|         |              | Mapping RAM Control Register                                        |          |

|         |              | Node Registers                                                      |          |

|         |              | Remote Command Register 1                                           |          |

|         |              | Remote Status Register                                              |          |

|         |              | Remote Command Register 2                                           |          |

|         |              | Adapter ID Register                                                 |          |

|         |              | Remote VMEbus Address Modifier Register                             |          |

|         |              | Remote IACK Read Registers                                          |          |

|         |              | ntroller Registers                                                  |          |

|         |              | DMA Controller and Error Status Registers Accessed From The PCI Bus |          |

|         |              | Local DMA Controller Command Register                               |          |

|         |              | Local DMA Packet Count Register                                     |          |

|         |              | Local DMA PCI Address Register                                      |          |

|         |              | Remote DMA Controller Remainder Count Register                      |          |

|         |              | Remote DMA VMEbus Address Registers                                 |          |

|         |              | S Slave Status Register                                             |          |

| Chapter |              | 4 Adapter Card                                                      |          |

| •       |              | ·                                                                   |          |

|         | 7.0 INTOQUE  | iondapter Card Jumper Blocks                                        | 83       |

|         |              | CSR                                                                 |          |

|         |              | RAM Window                                                          |          |

|         |              | t RAM Window                                                        |          |

|         |              | System Controller Mode                                              |          |

|         |              | Adapter Card LEDs                                                   |          |

|         |              | E64 Adapter Card Functions                                          |          |

| -       | -            |                                                                     |          |

|         |              | ionion                                                              |          |

|         |              | DI Mamary                                                           | 89<br>80 |

|         |      |              | Remote RAM Jumpers                                    |     |

|---------|------|--------------|-------------------------------------------------------|-----|

|         |      |              | Interaction With Mapping Registers                    |     |

|         |      |              | Dual Port RAM                                         |     |

|         |      |              | CI Accesses                                           |     |

|         | 8.5  |              | Interrupts                                            |     |

|         |      | 8.5.1        | Programmed Interrupts                                 | 91  |

|         |      |              | 8.5.1.1 Sending PT Interrupts                         | 91  |

|         |      |              | 8.5.1.2 Receiving PT Interrupts                       | 92  |

|         |      |              | 8.5.1.3 Sending PR Interrupts                         | 92  |

|         |      |              | 8.5.1.4 Receiving PR Interrupts                       | 92  |

|         |      | 8.5.2        | Error Interrupts                                      | 93  |

|         |      | 8.5.3        | DMA Interrupts                                        | 93  |

|         |      | 8.5.4        | Sending Backplane Interrupts To PCI                   | 94  |

|         |      | 8.5.5        | Writing An ISR                                        | 94  |

|         | 8.6  | Initiating A | ADMA Operation                                        | 95  |

|         |      | 8.6.1        | PCI Initialization                                    | 95  |

|         |      | 8.6.2        | DMA CSRs                                              | 96  |

|         |      | 8.6.3        | Other CSRs                                            | 97  |

|         |      | 8.6.4        | When Is The DMA Operation Done?                       | 97  |

|         |      |              | 8.6.4.1 DMA Done Interrupt                            | 97  |

|         |      |              | 8.6.4.2 Polling For DMA Done Bit                      | 98  |

|         |      | 8.6.5        | Programming Sequence For Initiating A DMA From VMEbus |     |

|         |      | 8.6.6        | Things To Remember                                    | 99  |

| Chapter | 9: ( | CSR Access   | ed From The VMEbus                                    | 101 |

|         |      |              | SR                                                    |     |

|         |      |              | e Registers                                           |     |

|         | 7.1  |              | Loopback Register                                     |     |

|         |      |              | Local Command Register                                |     |

|         |      |              | Local Status Register                                 |     |

|         |      |              | Address Modifier Register                             |     |

|         |      |              | Interrupt Vector Register                             |     |

|         | 92   |              | ode Registers                                         |     |

|         | 7.2  |              | Remote Command Register                               |     |

|         |      |              | Remote Status Register                                |     |

|         |      |              | PCI Adapter ID Register                               |     |

|         | 9.3  |              | troller Registers                                     |     |

|         | ,,,  |              | DMA Controller Registers Accessed From The VMEbus     |     |

|         |      |              | Local DMA Controller Command Register                 |     |

|         |      |              | Local DMA Remainder Count Register                    |     |

|         |      |              | Local DMA VMEbus Address Register                     |     |

|         |      |              | Local DMA Packet Count Registers                      |     |

|         |      |              | Remote DMA Remainder Count Register                   |     |

|         |      |              | Remote DMA PCI Address Registers                      |     |

| Chapter | 10:  | Setting The  | e VME64 Adapter Card Jumpers                          | 111 |

| eda.e.  |      | _            | ion                                                   |     |

|         |      |              | ation Notes                                           |     |

|         |      |              | Adapter Card Factory Settings                         |     |

|         |      |              | Adapter Card Jumper Blocks                            |     |

|         | 10.  |              |                                                       |     |

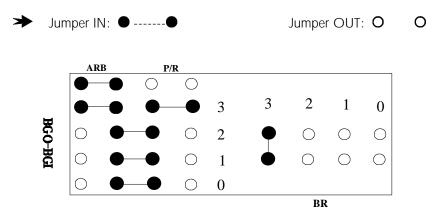

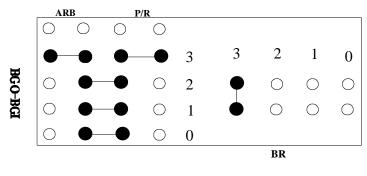

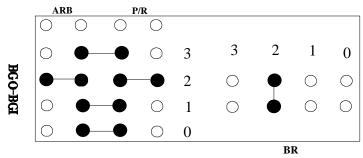

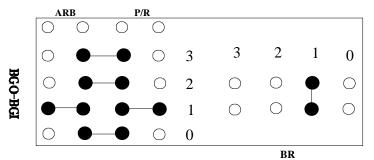

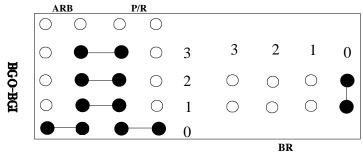

|         |      | 10 3 1       | System Jumpers                                        | ココン |

|             | 10.3.2 Bus Grant And Bus Request Jumpers                                          | 112 |

|-------------|-----------------------------------------------------------------------------------|-----|

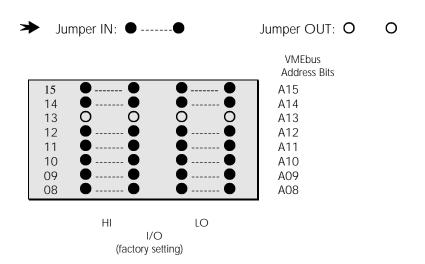

|             | 10.3.3 I/O Range Jumpers                                                          |     |

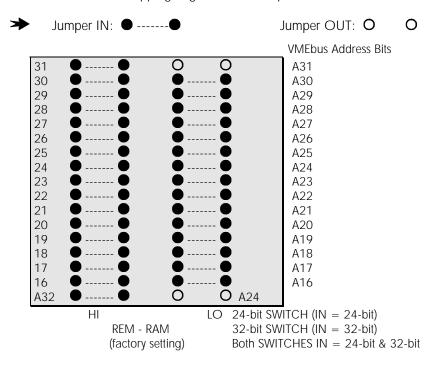

|             | 10.3.4 Remote RAM Jumpers                                                         |     |

|             | 10.3.5 Dual Port RAM Jumpers                                                      |     |

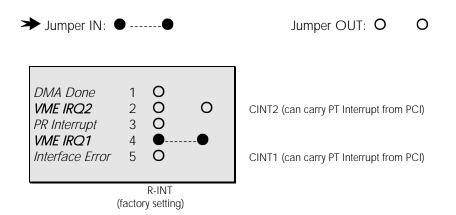

|             | 10.3.6 Transmitted Interrupt Jumpers                                              |     |

|             | 10.3.7 Received Interrupt Jumpers                                                 |     |

|             | 10.3.8 Address Bias Jumpers                                                       |     |

| 10.4        | Setting Jumpers For System Controller Mode                                        |     |

| Chapter 11: | Common Problems                                                                   | 123 |

| 11.0        | Introduction                                                                      | 123 |

| 11.1        | Software Problems                                                                 | 123 |

|             | 11.1.1 Data Order Is Incorrect                                                    | 123 |

|             | 11.1.2 Dual Port RAM Alignment                                                    | 123 |

|             | 11.1.3 Bus Error Or Unexpected Status ID (Interrupt Vector) Returned When Reading |     |

|             | IACK Read Register                                                                | 124 |

|             | 11.1.4 Programming Issues                                                         | 124 |

|             | 11.1.4.1 Volatile                                                                 |     |

|             | 11.1.4.2 Accessing Addresses Above One Megabyte                                   |     |

|             | 11.1.4.3 Making D32 Accesses                                                      | 125 |

| 11.2        | Pardware Problems                                                                 |     |

|             | 11.2.1 Using The VME64 Adapter Card LEDs As Diagnostic Tools                      |     |

|             | 11.2.2 Error In The Local Status Register                                         |     |

|             | 11.2.2.1 Local Status Register Bit 7: Interface Data Error                        |     |

|             | 11.2.2.2 Local Status Register Bit 6: Remote Bus Error                            |     |

|             | 11.2.2.3 Local Status Register Bit 2: Interface Timeouts                          |     |

|             | 11.2.2.4 Local Status Register Bit 0: Cable Disconnected                          |     |

|             | 11.2.3 PCI Motherboards                                                           |     |

|             | 11.2.3.1 Cache                                                                    |     |

|             | 11.2.3.2 PCI Slots                                                                | 129 |

|             | 11.2.3.3 Concurrent Accesses                                                      | 129 |

| Appendix A: | Glossary                                                                          | 131 |

| Appendix B: | VMEbus References                                                                 | 135 |

|             | VMEbus Pin Assignments                                                            |     |

| B.2         | VMEbus Address Modifier Codes                                                     | 137 |

| Index       |                                                                                   | 139 |

# Chapter 1: Introduction

#### 1.0 Overview

The 8xx VME64 adapters -- the next generation for SBS' market accepted and widely used bus adapters – are the most cost-effective solutions for applications requiring VME64 to VME64 to VME64 to PCI (PCI, CompactPCI or PMC) connectivity and fiber-optic capabilities. Applications written for SBS 617 and 618 adapters can easily port to 8xx adapters. The 8xx adapters deliver double the throughput of the earlier adapters by supporting D64 transactions on both VME and PCI.

With 8xx you can use a standard PC or workstation instead of a single board computer thereby letting you take advantage of a wealth of off-the-shelf software, the latest processor technology, and worldwide support form major PC, workstation and operating system manufacturers. Consequently, effectively speeding your development effort and reducing time to market.

The adapter's fiber-optic features make it ideal for environments requiring noise immunity, high-performance, electrical safety, isolation and long distance system separation.

The 8xx adapter allows you to share memory and special purpose boards between a PCI Local Bus computer and a VME64 system. The adapter provides high-speed data transfers between systems, and requires minimal software support.

The adapter interconnects two systems at the physical layer. Working at the lowest level, the bus, the adapter allows the two systems to share memory; memory appears to and is treated by each system as if it were its own. Therefore, a card only available on one bus may be accessed and directly controlled by a system using another bus. For example, an Array Processor board in a VME chassis can be directly controlled by the processor on a PCI bus.

Model 8xx supports two methods of intersystem communications: Memory Mapping and Direct Memory Access (DMA). Memory Mapping supports bi-directional random access bus mastering from either system. This allows Programmed Input/Output (PIO) access to VME RAM, dual-port memory, and VME I/O, and provides an easy-to-use, flexible interface with low overhead. A PCI bus master can access memory in the VME system through a window in PCI memory address space. Conversely, a VME bus master can access PCI memory from a window in VME address space.

Memory mapping is accomplished through 16,384 Mapping Registers that are used to steer memory accesses on one bus to the appropriate address on the other bus. The Mapping Registers allow PCI devices to access up to 32M bytes of VME address space and VME devices to access up to 16M bytes of PCI space. In addition, the Mapping Registers allow up to 16M byte DMA transfers.

Controller Mode DMA uses the adapter's DMA Controller to provide high-speed data transfers from one system's memory directly into the other system's memory. Data transfer can be initiated in both directions by either the PCI or VME processor. Each DMA cycle supports transfer lengths up to 16M bytes. The DMA Controller also allows memory-to-memory transfers between PCI memory and Dual Port RAM on the VME64 adapter card. Controller Mode DMA can sustain data rates up to 70 Megabytes per second (M Bytes/sec).

The 8xx adapter does not link the timing of the two buses (so that activity on one bus slows down the other). Instead, the adapter permits each bus to operate *independently*. The buses are linked only when a memory or I/O reference is made to an address on one system that translates to a reference on the other system's bus.

The adapter consists of two cards that are connected by fiber-optic cable that purchased separately. Cable is available from SBS in standard 5-meter or 10-meter lengths. Custom lengths may be ordered.

An optional Dual Port RAM card that installs on the VME64 adapter card is available from SBS. The Dual Port RAM can be accessed by both systems and provides an inexpensive method of expanding PCI and VME memory as well as a convenient way to share memory between the two systems. The following Dual Port RAM sizes are available: 128K and 8M bytes.

# 1.1 Adapter Features

### **Bus Communication Specifics:**

Both adapter cards are capable of remote bus mastership and allow simultaneous communication between the two chassis (except when a DMA transfer is in progress).

The PCI adapter card responds to and generates A32 memory and I/O accesses and supports D64, D32, D16, and D8 data widths (Mapping Registers and CSRs support only D32, D16). The PCI card supports delayed transactions so that the PCI bus is not occupied during accesses across the cable.

The VME64 adapter card responds to and generates A32, A24, and A16 accesses and supports D64, D32, D16, and D8 data widths (A16 space supports only D16 and D8). D32 and D64 Block Mode transfers are also supported.

The VMEbus adapter card accepts and can generate address modifier codes except A64, A40 and 2eVME.

System Controller: The VME64 adapter card can provide the system clock, reset, and bus error timeout feature.

Bus Arbitration: Provides Single-Level (SGL) or four-level Priority/Round-Robin (PRI/RRS) arbitration.

VME: Release-On-Request (ROR);

Release-On-Bus-Clear.

#### Access Times:

PCI bus read/write access to remote RAM: about 1.8 µsec.

PCI bus read/write access to remote Dual Port RAM: about 1.7 usec.

VME read/write access to local Dual Port RAM: 400 nsec.

### **DMA Controller Transfer Rate\*:**

\* This rate may vary significantly depending on PCI chip set implementation.

The adapter is capable of D64 sustained DMA data rates of:

70M Bytes/sec with 20 nsec Block Mode VMEbus memory cards;

40M Bytes/sec with 50 nsec Block Mode VMEbus memory cards;

20M Bytes/sec with 200 nsec Block Mode VMEbus memory cards;

25M Bytes/sec DMA from PCI bus to Dual Port RAM.

Actual data rates measured from the application software level are also dependent on the clock frequency of the PCI I/O channel controller and system software overhead.

DMA data transfer block length: 4 bytes to 16M bytes.

### Interrupt Passing:

All seven VMEbus interrupts can be passed to the PCI system.

Two types of programmed interrupts (PT and PR Interrupts) can be exchanged between the PCI adapter card and the VMEbus.

### Interrupt Acknowledgment:

RORA (Release On Register Access).

PCI acknowledgment of VMEbus interrupts and VMEbus vector passing is provided through an adapter card control register.

#### PCI - VMEbus Timeout:

PCI bus to VMEbus transfer cycles timeout within 30  $\mu$ sec. This results in an error bit being set and an interrupt generated if enabled.

#### Conformance:

The VME64 adapter card meets IEEE 1014C specifications.

The PCI card meets the PCI Local Bus specification version 2.1.

# Power Requirements:

The VME64 adapter card draws 2.5A at 5V.

The PCI adapter card draws 1.5A at 5V.

#### **Environment:**

Temperature:  $0^{\circ}$  to  $+60^{\circ}$  C operating;

$-40^{\circ}$  to  $+85^{\circ}$  C storage.

Humidity: 0% to 90% non-condensing.

### 1.2 Supporting Products

Cables to connect the two adapter cards, and Dual Port RAM cards are also available from SBS. Please call 651-905-4700 for more information.

#### 1.2.1 Cables

Fiber-optic cables to connect the two adapter cards consist of  $50 \mu m$  multimode fiber with a duplex SC connector for the PCI card and an LC connector for the VME64 card, or for the Model 800 two LC connectors. Cables are available in 5-meter and 10-meter lengths. Custom-length cables up to 500 meters are also available from SBS. *All cables are purchased separately.*

#### 1.2.2 Dual Port RAM

Dual Port RAM is an optional memory card that attaches to the VME64 adapter card and appears to both systems as simply more memory. The address of the Dual Port RAM is independently set on each adapter card, and may be set to respond to one address range in one system and a different range in the other. Both systems can access the memory at the same time with the VME64 adapter card arbitrating simultaneous accesses.

SBS' Dual Port RAM is a printed circuit card that plugs into the VME64 adapter card as a daughter card. The following memory sizes are currently available: 128K and 8M bytes.

### 1.3 System Controller Operation

The adapter can act as a link between a PCI chassis and a VMEbus chassis even when the VMEbus chassis has no processor or system controller present. This form of operation is called System Controller Mode.

System Controller Mode is configured by setting the VME64 adapter card's SYS jumper block to drive the system clock (SYSCLK) and the Bus Error (BERR) global timeout. The SBS VME64 adapter card may be configured to be a Single-Level (SGL) bus arbiter or a four-level bus arbiter in Priority (PRI) or Round-Robin (RRS) mode.

### 1.4 Adapter Control And Status Registers (CSRs)

The CSRs allow PCI and VME bus masters to control and obtain status information about the adapter. Each card has CSRs that can be accessed locally and CSRs that can be accessed remotely.

### 1.5 Direct Memory Access (DMA)

DMA is the transfer of data from one memory address to another without processor intervention once the transfer starts. DMA logic is usually employed when large files or sections of data need to be moved.

The adapter supports Controller Mode DMA. In Controller Mode DMA, the adapter becomes a bus master on both the PCI bus and the VME bus, and transfers data from memory on one system to memory on the other system. Controller Mode DMA transfers require very little processor attention and are a very fast means of transferring data.

#### 1.6 Interrupts

The adapter has four sources of interrupts; three can be generated by either adapter card, one is unique to the PCI adapter card.

#### Common interrupt sources:

- Programmed Interrupts Each adapter card can receive and send a programmed interrupt from the other adapter card. Programmed interrupts are the basic method processors on two dissimilar buses use to communicate and synchronize data transfers. There are two types of programmed interrupts: Programmed interrupt to Transmitter (PT) and Programmed interrupt to Receiver (PR).

- Interface Error Interrupt Each adapter card can assert an interrupt when it detects that an error occurred.

- DMA Done Interrupt Each adapter card can interrupt a local processor when the DMA has completed.

PCI adapter card specific interrupt source:

■ VME Backplane Interrupt - The PCI adapter card can interrupt the PCI bus whenever any of seven VME interrupt levels are asserted. The adapter also allows a PCI processor to acknowledge the VME interrupt and retrieve the interrupt acknowledgment vector.

## 1.7 Mapping Registers

The PCI adapter card is equipped with Mapping Registers that allow the adapter to take a large contiguous section of local memory and map it to many small non-contiguous sections of remote memory. This feature is very desirable because most of today's system architectures use virtual and paged memory management schemes. These schemes often satisfy an application's memory request with small sections of memory that are scattered throughout the memory space. The Mapping Registers allow a bus-to-bus bridge to remap these non-contiguous memory areas into a contiguous areas on the remote bus. This mapping works both for PCI to VME accesses and VME to PCI accesses.

# Chapter 2: Getting Started

Make sure you follow proper ESD handling procedures (refer to EIA-625, ESD Association Handbook, or MIL-HDBK-263) when working with cards and components.

## 2.0 Unpacking

The SBS 8xx adapter package contains the following items. Please identify each item and notify SBS (651-905-4700) if any are missing.

#### Two card adapter sets:

■ Model 800:

Two VME64 adapter cards -- Part Number: 85913153

■ Model 810:

One VME64 adapter card -- Part Number: 85913153

One PCI adapter card -- Part Number: 85911025

■ Model 820:

One VME64 adapter card -- Part Number: 85913153

One PMC adapter card -- Part Number: 85912465

■ Model 830:

One VME64 adapter card -- Part Number: 85913153

One CompactPCI adapter card -- Part Number: 85912115

Software Drivers CD-ROM -- Part Number: 85702000

VME64 Adapters manual -- Part Number: 85913163

One I/O cable to connect the two cards (purchased separately)

### Single card only:

800-202 VME64 card -- Part Number: 85913153

810-201 PCI card only -- Part Number: 85911025

820-203 PMC only -- Part Number: 85912465

830-204 CompactPCI card only -- Part Number: 85912115

➤ Eight-digit part numbers with card revision level are printed on white labels affixed to the adapter cards.

### 2.1 Help!

Please have the following items and information handy when calling SBS for technical support:

- Model number and revision level of the adapter, or the serial number located on the white bar code label on the adapter cards.

- Size of Dual Port RAM, if any.

- Configuration information including jumper settings on the VME64 adapter card.

- This manual.

Technical support is available from 9:00 a.m. - 5:00 p.m. (Central Time) Monday - Friday, excluding holidays.

#### Contact SBS at:

Mailing Address: SBS Technologies, Inc.

1284 Corporate Center Drive St. Paul, MN 55121-1245

Phone: 651-905-4700 Fax: 651-905-4701

Email: support.commercial@sbs.com

Web: www.sbs.com

#### 2.2 Installation

Observe static safety precautions to prevent damage to the cards.

Make sure power is off before installing cards.

### 2.2.1 Configure The Adapter Cards

Any required jumper configuration takes place before the adapter cards are installed. Refer to Chapter 10 for information about configuring the VME64 card. There are no jumpers to configure on the PCI adapter card.

### 2.2.2 Installing The PCI Adapter Card

- 1. Locate a vacant PCI card slot in the PCI chassis that supports a bus master.

- 2. Remove the metal plate that covers the cable exit at the rear of the chassis.

- 3. Insert the PCI adapter card into the connector.

- 4. Fasten the adapter card in place with the mounting screw.

### 2.2.3 Installing The VME64 Adapter Card

- > VME backplanes have jumpers to connect the daisy-chained, bus grant and interrupt acknowledge signals around unused card locations. Make sure these jumpers are removed from the slot in which the adapter card will be installed.

- 1. Decide if the VME64 adapter card is the system controller. If it is, it must be installed in slot 1.

- 2. Locate an unoccupied 6U slot\* in the VME card cage if the adapter card is not the system controller.

- 3. Insert the card into the connector of the selected slot.

### 2.2.4 Connecting The Adapter Cable

- \*\* Keep the ends of the fiber-optic cable clean. Use alcohol-based fiber-optic wipes to remove minor contaminants such as dust and dirt.

- Fiber-optic cables are made of glass; therefore, they may break if crushed or bent in a loop with less than a 2-inch radius.

#### To connect the I/O cable:

- 1. Make sure the PCI computer system and the VME chassis are powered off.

- 2. Remove the rubber boots on the fiber-optic transceivers as well as the ones on the fiber-optic cables. Be sure to replace these boots when cables are not in use.

- 3. Plug one end of the fiber-optic cable into the PCI adapter card's transceiver.

- 4. Plug the other end of the fiber-optic cable into the VME64 adapter card's transceiver.

- Turn power on to both PCI and VME systems.

- After installation, make sure the READY LEDs on both adapter cards are lit. They must be on for the adapter to operate.

#### 2.3 Additional References

- The *VMEbus Specification Manual* is available from VITA (VMEbus International Trade Association), 7825 E. Gelding Drive, Suite 104, Scottsdale, AZ 85260-3415.

- *IEEE Standard 1014* is available from The Institute of Electrical and Electronics Engineers (IEEE), 445 Hoes Lane, Piscataway, NJ 08855-1331.

- *The PCI Local Bus Specification* is available from the PCI Special Interest Group, JF2-51, 5200 NE Elam Young Parkway, Hillsboro, OR 97124-6497.

- *PCI BIOS Specification* is available from the PCI Special Interest Group, JF2-51, 5200 NE Elam Young Parkway, Hillsboro, OR 97124-6497.

- DOS Protected Mode Interface (DPMI) Specification Version 1.0 is available from Intel Corp.

- Data Format and Bus Compatibility in Multiprocessors, IEEE Micro, August 1983, is available from IEEE Micro, PO Box 3014, Los Alamitos, CA 90720-1264.

# Chapter 3: VME64 to PCI Adapters

#### 3.0 Introduction

The 810, 820 and 830 adapters function as bridges between a PCI bus and a VMEbus. The adapter allows PCI bus masters to become masters on the VMEbus, and VME bus master to become masters on the PCI bus.

Because these adapters interconnect two dissimilar buses, it is important to understand both buses. Chapter 3 discusses basic bus issues, features that are common to both adapter cards, and cable conflict issues.

#### 3.1 PCI Bus

The PCI bus is a 64/32-bit architecture designed for high-data throughput, self-configuration, and multiple bus mastership.

The PCI bus is self-configuring; therefore, all PCI devices are automatically configured by the startup firmware at system boot. The startup firmware sets up interrupt level routing and other hardware parameters, and resolves all addressing conflicts. Simply plug the PCI device into an open PCI slot and switch on the power; the system takes care of configuration.

The PCI specification supports multiple bus masters on the PCI bus. Consequently, the adapter allows VMEbus masters to become bus masters on the PCI bus, and supports Direct Memory Access (DMA) data transfers.

### 3.2 VMEbus

The VMEbus is a bus that is widely used in industrial, commercial and military applications worldwide. An abundance of VME cards are available to perform a wide range of tasks, from digital image processing to disk controllers. Like the PCI bus, the VMEbus supports multiple bus masters and high data transfer rates. Unlike the PCI bus, the VMEbus is not self-configuring.

A VMEbus consists of card cage with 1 - 21 slots, a backplane with two connectors and, normally, five jumpers per slot. The slots are numbered from 1 - 21. Slot 1 is the system controller slot. Cards with different functions are inserted in the slots to form a customized VME chassis.

Sections 3.2.1 - 3.2.4 discuss several important unique VME features: system controller operation, backplane jumpers, interrupt acknowledgment cycle, and address spaces.

### 3.2.1 System Controller Operation

A card that provides system controller functions must be installed in slot 1 of the VME card cage. The system controller (usually a processor card) provides bus arbitration, checks for timeouts, and drives the system clock and system reset signals. The SBS VME64 adapter card may be configured to be a Single-Level (SGL) bus arbiter or a four-level bus arbiter in Priority (PRI) or Round-Robin (RRS) mode.

The adapter has the ability to act as a link between a PCI chassis and a VME chassis even when the VME chassis has no processor present. This form of operation is called System Controller Mode. System Controller Mode is

selected on the VME64 adapter card by configuring the SYS and BGO-BGI jumper blocks. These jumpers tell the VME64 adapter card that it must provide the system controller functions, including: bus arbitration, timeout detection, and system level signals. See Chapter 10 for detailed descriptions of VME64 adapter card jumper blocks.

A priority arbiter provides requesters preferential control of the data transfer bus over the other levels. By definition, BR3 is the highest priority, and BR0 is the lowest. When two or more requests are pending, the arbiter assigns control of the bus in the appropriate order by granting the bus in this sequence.

The priority arbiter must assert BCLR when a bus master of higher priority than the one in control of the bus initiates a request. When BBSY is asserted and a request is pending, the arbiter will drive BCLR if the pending request is of higher priority than the bus grant of the previous arbitration. Although the current bus master is not required to relinquish control of the bus in any prescribed time limit, it can continue transferring data until it reaches an appropriate stopping point.

A round-robin arbiter gives equal priority to all bus request levels. It grants control of the bus on a rotating basis. Upon release of the bus, the arbiter steps one level and tests for an active request and asserts a bus grant. If no request is active, it continues stepping through the levels until a request is found.

The RRS arbiter can drive the BCLR signal. In RRS mode BCLR is asserted whenever a master requests the bus on a level other than the last one granted. It does not assert BCLR if a master on the same level requests the bus.

- There must be one and only one card with System Controller Mode enabled. This card must be installed in slot 1.

- When the VME64 adapter card is in System Controller Mode, except in special situations, the SYSCLK and SYSRESET jumpers must be installed. In most cases, the Detect Bus Timeout jumper should also be installed.

#### 3.2.2 Backplane Jumpers

VME chassis have five jumpers associated with each slot except slot 1. The five jumpers pass the bus grant and interrupt acknowledge signals to the next slot. If a slot is empty, the jumpers must be installed in order to pass the daisy-chained signals to the next slot. For example, if slots 1, 5 and 7 have cards installed, slots 2, 3, 4, and 6 must have the backplane jumpers installed or the system will not function properly.

- If a slot has no card installed and a card is installed in higher number slot, the backplane jumpers must be installed in the empty slot.

- → Backplane jumpers should never be installed in slots in which cards are installed.

#### 3.2.3 VMEbus Address Modifiers

The VMEbus specification defines three types of address spaces: extended (A32), standard (A24) and short (A16). Extended (A32) addressing uses 32 address bits. Standard (A24) addressing uses 24 address bits. Short (A16) addressing uses 16 address bits. The VMEbus uses special lines, the address modifier lines, to select which type of address space is being referenced.

Each address space is independent of the other address spaces and can be thought of as a logically separate address bus. A32 addressing uses address lines A31-01. A24 uses A23-01, and A31-24 are unused. A16 uses A15-A01, and A31-16 are unused. The VMEbus does not have an address 0 (A0) line. Byte addressing is controlled by the signals DS0 and DS1. Address lines AO3-AO1 are used during Interrupt ACKnowledge cycles (IACK cycles).

| The following table summarizes the use of the address bus | The following | table | summarizes | the | use | of | the | address | bus. |

|-----------------------------------------------------------|---------------|-------|------------|-----|-----|----|-----|---------|------|

|-----------------------------------------------------------|---------------|-------|------------|-----|-----|----|-----|---------|------|

| ACTIVE PORTION OF ADDRESS BUS - ADDRESS ROUTING |                   |                   |           |                    |  |

|-------------------------------------------------|-------------------|-------------------|-----------|--------------------|--|

| A31 - A24                                       | A23 - A16         | Address Modifier  |           |                    |  |

|                                                 |                   |                   |           | Codes (hex)        |  |

| A31                                             |                   | Extended (32-bit) |           |                    |  |

|                                                 |                   | 08 - 0F           |           |                    |  |

|                                                 | Standard (24-bit) |                   |           |                    |  |

|                                                 |                   | 38 - 3F           |           |                    |  |

| A15A01                                          |                   |                   |           | Short I/O (16-bit) |  |

|                                                 |                   |                   |           | 29, 2D             |  |

|                                                 |                   |                   | A03 - A01 | Interrupt          |  |

|                                                 |                   |                   |           | Acknowledge        |  |

= Unused portion of address bus.

The value of the address modifier lines, AM[0..5], determines which address space is used. The VMEbus master is responsible for supplying the proper address modifier at the same time it drives the address lines. Slaves are designed to respond to cycles with a particular address modifier; however, most slaves are capable of responding to several address modifiers.

The address modifier generated when the PCI bus accesses the VMEbus is determined by the value in the selected Mapping Register. The programmer should determine which address modifier the target slave responds to, then program the Mapping Registers with that value.

The most commonly used address modifier codes are listed below. For a complete list of address modifiers, see Appendix B.

| ADDRESS MODIFIER (HEX) | NUMBER OF ADDRESS BITS | TRANSFER TYPE                              |

|------------------------|------------------------|--------------------------------------------|

| 2D                     | 16                     | Short supervisory access                   |

| 3C                     | 24                     | Supervisory 64-bit block transfer          |

| 3D                     | 24                     | Standard supervisory access                |

| 3F                     | 24                     | Standard supervisory block transfer        |

| OC OC                  | 32                     | Extended supervisory 64-bit block transfer |

| OD                     | 32                     | Extended supervisory data access           |

| OF                     | 32                     | Extended supervisory block transfer        |

The VME64 adapter card can generate and respond to all address modifiers except A64, A40, and 2eVME.

#### 3.2.4 VMEbus Interrupts And The IACK Cycle

Hardware devices use interrupts to indicate that they need attention or that some event has occurred. The VMEbus supports seven interrupt levels labeled IRQ1 to IRQ7. Any number of devices can use the same interrupt; however, only one VME device can respond to an interrupt level.

Interrupts are responded to with an IACK cycle. The basic interrupt process is as follows:

- 1. A VME device asserts one of the seven interrupt lines. For this example, we assume IRQ1.

- 2. The VME device acknowledging IRQ1 receives control of the VME and starts a byte, word, or longword read with the IACK signal asserted. This read should have address bits A3 A1 equal to the level of the interrupt to be acknowledged. For example, IRQ1 is acknowledged by reading from location 2 (A3=0, A2=0, A1=1).

- 3. The system controller starts the IACK daisy-chain by sending IACKIN to slot 2. This daisy-chained IACK signal is passed up the slots until it reaches the card asserting IRQ1.

- 4. The device asserting IRQ1 responds to the IACK read cycle with the appropriate size data (the status/id value or IACK read vector).

- 5. The VME device uses the IACK read vector to determine which device is interrupting and makes any necessary accesses to the interrupting device's registers to acknowledge the interrupt.

Two types of interrupting devices are supported by the VMEbus: Release On AcKnowledgment (ROAK) and Release On Register Access (RORA). A ROAK device removes its interrupt near the end of the IACK cycle (see step 4 above). A RORA device removes its interrupt after the IACK cycle occurred and one of its registers is accessed (see step 5).

For RORA devices, software must make a register access to switch off the interrupt before exiting the Interrupt Service Routine (ISR). Otherwise, the interrupting device will not remove its interrupt and the processor will go into an endless IACK loop.

### 3.3 Bridging PCI And VMEbus

The PCI and VME64 adapter cards are connected by a cable that carries commands from one card to the other. Unless there is a software cable control scheme, it is possible for both cards to send commands at the same time. Since the PCI bus supports retry and the VMEbus (Rev. C) does not, the PCI adapter card usually gives precedence to VME commands. The adapter responds to the PCI bus master with a target retry response and allows the VME command to proceed. Ideally, the retried PCI bus operation follows. The single exception, a local register access, momentarily preempts all VME commands.

Even though the PCI bus supports retry, resolution of command collisions or cable conflicts may not be achieved on all PCI systems. This is not a design flaw with either the adapter or the PCI system. The PCI specification is not defined to fully accommodate add-in cards that bridge to buses that do not have retry. Signals that resolve collisions are not available on the PCI connector. These signals, sideband signals, exist only between PCI bus components soldered directly to the motherboard. Sideband signals' functional definition is beyond the control of the PCI specification.

Command collisions to add-in board bridges can be accommodated by PCI systems if all processor initiated PCI bus requests are designed to back-off in the presence of a request from an add-in board. PCI systems that do not function in this manner exhibit bus livelock. Some workstations function free of bus livelock. Conversely, most personal computers exhibit bus livelock.

PCI bus livelock takes on two separate forms. The first occurs when the CPU becomes a PCI bus master and attempts to access the PCI adapter card. The PCI adapter card issues a target retry response because of a pending VME command. When the PCI adapter card becomes bus master, it too receives a target retry response. Bus traffic momentarily consists of continuous retry responses from the PCI adapter card and the PCI system memory bridge. The second situation begins with the CPU becoming a bus master, and attempting to access the PCI adapter card. The PCI adapter card activates the bus request signal, attempting to become bus master, but is never granted access to the PCI bus. Bus traffic momentarily consists of continuous retry responses from the PCI adapter card. In either case, the PCI adapter detects bus livelock and returns an error response to the VME64 adapter card. There is no alternative in either case but to activate the BERR\* signal on the VMEbus. The CPU initiated operation to the PCI adapter will complete.

Installation of the PCI adapter card behind a PCI-to-PCI Bridge (PPB) presents additional potential for bus livelock. Specifically, if write posting is enabled in the PPB and the posted write buffer contains data, any read command from the PCI adapter card will be continually retried until the buffers are flushed. If the destination of the posted write buffer is the PCI adapter card, momentary bus livelock will occur. Upon detection of this condition, the PCI adapter card returns an error status back to the VME64 adapter card, ultimately activating the BERR\* signal on the VMEbus.

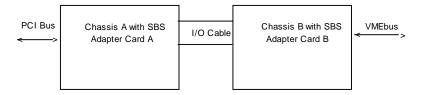

Two terms that deal with cable control are used throughout this manual: Transmitter and Receiver. When a card sends a command, it is a Transmitter. When a card receives a command, it is a Receiver.

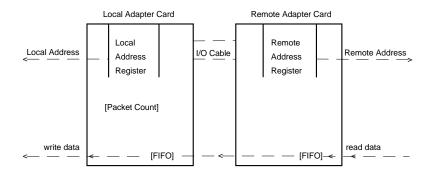

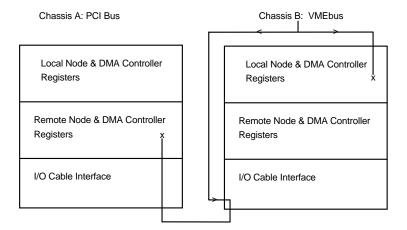

For example (see diagram above) --

Assume a device in chassis A performs reads or writes to memory or I/O on chassis B, but devices in chassis B never perform reads or writes to cards inside chassis A. In this case, adapter card A would be the *transmitter* and adapter card B would be the *receiver*.

The adapter uses two methods of passing software or programmed interrupts between adapter cards: Programmed interrupts to Transmitter (PT Interrupts) and Programmed interrupts to Receiver (PR Interrupts). Because the adapter has hardware cable conflict resolution, either method may be used without concern for cable conflicts.

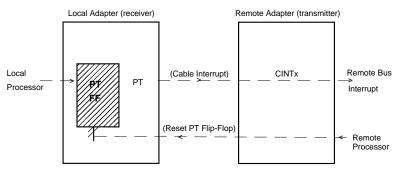

### 3.3.1 Programmed Interrupt To Transmitter (PT)

The PT Interrupt allows an adapter card to *generate* an interrupt on the other adapter card's bus without making a remote cable access.

A local processor sets the Send PT Interrupt bit in a local adapter CSR. Adapter hardware then sends this interrupt request to the remote adapter card using a Cable Interrupt (CINT) line. The remote processor can then acknowledge the PT Interrupt by writing a remote adapter CSR.

Programmed Interrupt To Transmitter

-- PT Interrupt --

See sections 5.5 and 8.5 for information on sending, receiving and acknowledging programmed interrupts.

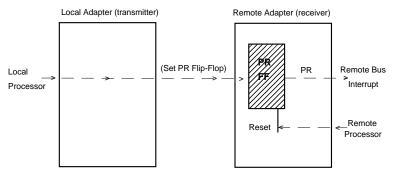

### 3.3.2 Programmed Interrupt To Receiver (PR)

The PR Interrupt allows an adapter card to *receive* an interrupt and acknowledge it without a remote cable access.

A local processor sets the Send PR Interrupt bit in a remote adapter CSR. This causes an interrupt to be asserted on the remote bus. The remote processor can then acknowledge the PR Interrupt by writing a local adapter CSR.

Programmed Interrupt To Receiver

-- PR Interrupt --

See sections 5.5 and 8.5 for information on sending, receiving and acknowledging programmed interrupts.

### 3.3.3 Direct Memory Access (DMA)

Direct Memory Access, DMA, is the transfer of data from one memory address to another *without* processor intervention once the transfer starts. DMA logic is usually employed when large files or sections of data need to be moved. DMA is a highly efficient way to move data because it does not require processor overhead.

The adapter supports Controller Mode DMA. In Controller Mode DMA, the adapter becomes a bus master on both the PCI bus and the VMEbus. Controller Mode DMA is used when the programmer wants the adapter to move a large block of data from one system to the other system. Transfer sizes from 4 bytes to 16M bytes are supported.

The DMA Controller is accessible from a VME or PCI processor through the adapter node I/O space. Consequently, a single processor can perform all DMA setup and start commands on both local *and* remote cards.

→ When a DMA is in progress, neither system may use any adapter features that require use of the cable; for example, remote node registers, remote Dual Port RAM, or remote memory.

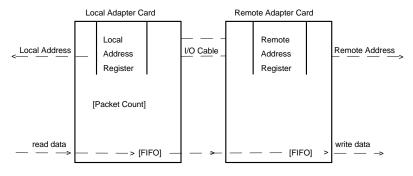

#### 3.3.4 How Controller Mode DMA Transfers Occur

Each adapter card has a DMA Controller. The DMA Controllers are somewhat independent of each other. While they are synchronized to pass data across the interface cable, they also independently perform reads and writes in their respective chassis.

The basic operations in a DMA transfer from local to remote memory (DMA write), once the DMA transfer has started, are as follows:

- 1. The local adapter card presents an address to its bus from the local address register and signals a read.

- The locally read data are stored in the local FIFO and the address register (a counter) increments.

- 3. When the FIFO has a complete packet of information, the data are sent to the remote FIFO and the packet counter decrements.

- 4. When the remote FIFO has a complete packet of information, the remote adapter card presents an address to the remote bus from the remote address register (also a counter) and signals a write. The data in the remote FIFO are written to its bus and the remote address register increments.

- 5. The packet transfer from the local adapter card to the remote adapter card continues until the local DMA packet count reaches zero.

DMA Controller Transfer From Local To Remote

-- DMA Write --

The adapter runs DMA transfers from remote to local (DMA read) in much the same way as described above. The remote bus controller begins by reading remote data and sending them from the remote FIFO to the local FIFO, where the local adapter card writes local FIFO data to local memory.

DMA Controller Transfer From Remote To Local

--DMA Read --

This form of DMA provides a very efficient, high-speed transfer because each bus is allowed to run at maximum speed. All data are moved without the intervention of a processor on either side of the adapter.

A DMA transfer (read or write) can be initiated from either system.

### 3.4 Accessing Windows

A window is a range of addresses that the adapter responds to for a specific function. The adapter uses windows to access adapter functions.

Each of the adapter's windows has two properties: a unique starting address and size. The window's starting address is called its base address and is the lowest numerical address that hits the window. The window's size is the number of bytes past the base address that the window extends.

When discussing the base address of a window, the address is given as a physical address, the address that appears on the bus. The physical address may or may not be the same as the address (virtual address) the programmer sees. Most of today's Operating Systems and machine architectures use some type of memory management system that translates virtual addresses into physical addresses. Most Operating Systems provide functions that, given a physical address and length, will map a virtual address to this space.

Throughout this manual, there are references to accessing a specific offset within a window. For example, write 0x80 to Remote Command Register 1 at offset 8. This instruction translates to write 0x80 to the physical address equal to the base of the Node Register Window plus 8.

Become familiar with the method your specific Operating System uses to map physical addresses to virtual addresses. To use the adapter, you will need to map many PCI adapter windows.

#### 3.5 Byte And Word Swapping

VME and PCI systems store and transfer data differently. VME systems store data in big endian format. PCI systems store data in little endian format. These differences cause data moved between the two systems to appear scrambled. For example, a PCI processor stores an integer differently than a VME processor, therefore, an integer transferred from one system to the other will be misinterpreted by the receiving processor. To resolve this problem, the adapter provides several methods of byte swapping.

Byte swapping incorporates three primary issues:

- The access size -- 8-bit, 16-bit or 32-bit;

- Little endian versus big endian;

- The data size -- 8-bit, 16-bit, or 32-bit.

#### 3.5.1 Data Accesses

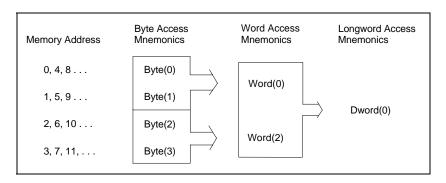

Most buses support multiple transfer widths. Both VMEbus and PCI systems support byte, word, and longword accesses. This manual uses shorthand notations for describing a particular byte, word or longword. Byte(0) refers to bytes stored at addresses that are multiples of four. Byte (1) is defined as the byte after Byte(0), and so forth up to Byte(3). Word(0) is a word with an even starting address; it is composed of Byte(0) and Byte(1). Word(1) has an odd starting address and is composed of Byte(1) and Byte(2). Dword(0) is composed of Word(0), Word(2) and Byte(0) - Byte(3).

Data stored in a specific memory location is also described using a shorthand notation. For example, instead of *0x55 is stored in memory address 0*, the shorthand notation is *Byte(0) is 0x55*.

Mnemonics for Data Accesses

### 3.5.2 Little Endian Versus Big Endian

There are two popular ways to store multiple byte data in memory: big endian and little endian.

Big endian architectures store multiple byte data in consecutive memory locations with the most significant byte at the lowest numerical addresses. In this case, Byte(0) holds the *most significant* byte.

Little endian architectures store multiple byte data with the least significant byte at the lowest numerical address. Byte(0) holds the *least significant* byte.

The VMEbus is oriented towards big endian processors. The PCI bus is oriented towards little endian processors.

| Data Type                        | Memory<br>Location | Little Endian<br>(PCI) | Big Endian<br>(VMEbus) |

|----------------------------------|--------------------|------------------------|------------------------|

| String "ABCD"                    | Byte(0)            | 'A'                    | 'A'                    |

|                                  | Byte(1)            | 'B'                    | 'B'                    |

|                                  | Byte(2)            | 'C'                    | 'C'                    |

|                                  | Byte(3)            | 'D'                    | 'D'                    |

| 32 Bit Integer 12345678          | Byte(0)            | 78                     | 12                     |

|                                  | Byte(1)            | 56                     | 34                     |

|                                  | Byte(2)            | 34                     | 56                     |

|                                  | Byte(3)            | 12                     | 78                     |

| 2 16 Bit Integers 1234, and 5678 | Byte(0)            | 34                     | 12                     |

|                                  | Byte(1)            | 12                     | 34                     |

|                                  | Byte(2)            | 78                     | 56                     |

|                                  | Byte(3)            | 56                     | 78                     |

Big Endian Versus Little Endian

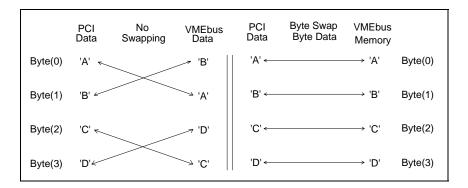

#### 3.5.3 Swapping For Byte Accesses

For byte accesses across the adapter, the byte order is swapped. For example, a PCI processor performs a byte write of Byte(0) in PCI memory to VMEbus. If no swapping bits are active, a VMEbus processor looks in Byte(1) for the byte that was transferred.

The adapter provides a Byte Swap On Byte Data bit that is used to correct the byte ordering problem when byte data are transferred across the adapter. When this bit is set, byte accesses across the cable are automatically swapped. For example, with the Byte Swapping On Byte Data bit set, a byte write of Byte(0) is stored in the remote memory's Byte(0).

Swapping for Byte Transfers of the String "ABCD"

- > Set the Byte Swap Byte Data bit when transferring byte data as bytes between the two systems.

- ➤ Word swap and byte swap on non-byte data have no effect on byte accesses through the adapter.

- → Byte data can be transferred as words or longwords if the Byte Swap On Non-Byte Data bit is set.

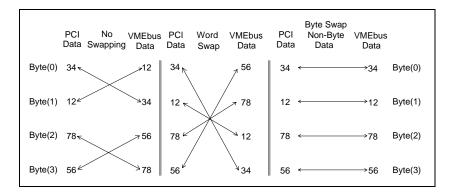

# 3.5.4 Swapping For Word Accesses

When words are transferred via the adapter, the byte order is swapped just like for byte transfers. Because the VMEbus is big endian and the PCI is little endian, this byte swapping is desirable. For example, PCI memory contains the two byte number 1234: Byte(0) is 0x34 and Byte(1) is 0x12. The PCI processor then writes this word to VME memory. If no byte swapping bits are set, the PCI adapter stores the data on the VMEbus as follows: Byte(0) is 0x12 and Byte(1) is 0x34.

If the default swapping is not acceptable to your application, the adapter provides two other swapping methods for word accesses: swapping adjacent words and byte swap on non-byte data. These two methods can be used alone or combined.

Word swap causes adjacent words to be swapped as they pass through the adapter. For example, if the PCI writes Byte(0) and Byte(1) as a word to the VMEbus, PCI Byte(0) is stored in VMEbus Byte(3) and PCI Byte(1) is stored in VMEbus Byte(2).

In Byte Swap On Non-Byte Data Mode, the individual bytes within the word are swapped as they pass through the adapter. For example, if PCI writes Byte(0) and Byte(1) as a word to the VMEbus, PCI Byte(0) is stored in VMEbus Byte(0) and PCI Byte(1) is stored in VMEbus Byte(1).

Swapping for Word Transfers of the Numbers 1234 and 5678

- No swapping bits need to be set if word data are transferred by bytes or words.

- → Byte swap on byte data has no effect on word accesses.

### 3.5.5 Longword Accesses

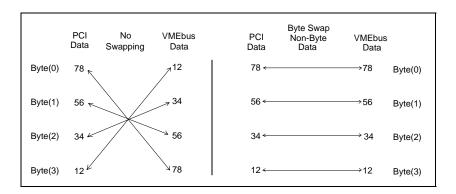

When longword accesses are made through the adapter, the byte order within the longword is reversed. For example, the longword 1234678 is stored in PCI memory as: Byte(0) is 0x78, Byte(1) is 0x56, Byte(2) is 0x34, and Byte(3) is 0x12. When this longword is transferred across the adapter, the bytes are completely swapped in VMEbus memory. VMEbus Byte(0) is 0x12, Byte(1) is 0x34, Byte(2) is 0x56, and Byte(3) is 0x78. Because the PCI bus and VMEbus are oriented towards different endian formats, this swapping is desirable.

Byte Swap on Non-Byte Data Mode is also available for longword accesses. In this mode, the byte ordering within each longword is maintained. A PCI value of 78563412 in PCI Byte(0) through Byte(3) is stored as 78563412 in VMEbus Byte(0) through Byte(3).

Swapping for Longword Transfers of the Number 12345678

- No swapping bits need to be set if longword data are transferred by longwords.

- → Byte swap on byte data and word swap have no effect on longword accesses.

#### 3.5.6 Access Width Versus Data Width

The following table shows how to set the Byte Swapping bit for different transfer lengths and different data sizes. This table assumes the PCI processor is little endian-based, and the VME processor is big endian-based.

|                | SIZE OF DATA                             |                                  |                                  |  |  |  |

|----------------|------------------------------------------|----------------------------------|----------------------------------|--|--|--|

|                | Byte Word Longword                       |                                  |                                  |  |  |  |

| SIZE OF ACCESS |                                          |                                  |                                  |  |  |  |

| Byte           | Set Byte Swap<br>Byte Data bit           | No swapping                      | Software<br>swapping<br>required |  |  |  |

| Word           | Set Byte Swap<br>On Non-Byte<br>Data bit | No swapping                      | Set Word Swap<br>bit             |  |  |  |

| Longword       | Set Byte Swap<br>On Non-Byte<br>Data bit | Software<br>swapping<br>required | No swapping                      |  |  |  |

Table of Common Byte Swapping Combinations

For more information about byte ordering and its history, we recommend the following article:

Data Format and Bus Compatibility in Multiprocessors, IEEE Micro, August 1983, PO Box 3014, Los Alamitos, CA 90720-1264.

# 3.6 Loopback

The adapter's loopback feature facilitates testing of the fiber-optic link. Loopback can be activated from either the PCI or VME side of the adapter by enabling the appropriate bits in either the PCI Loopback Control Register (see section 6.1.6) or the VMEbus Loopback Register (see section 9.1.1). The two loopback registers each contain a bit to enable local loopback and a bit to enable remote loopback. Together the local and remote loopback bits allow the adapter's data path to loopback in one of three ways:

- 1. Local loopback with the data path looped on the local card. This method requires only the Enable Local Loopback bit of the adapter's activating side's loopback register to be set to "1" (high active).

- 2. Remote loopback with the data path looped via fiber wrap-around. This method requires that the Enable Remote Loopback bit be set to "1" (high active) in the activating side's loopback register and that the transmitting fiber of the activating side be wrapped back to its receive port.

- 3. Remote loopback with the data path looped on the remote card. This method requires only the Enable Remote Loopback bit of the adapter's activating side to be set to "1" (high active). In this method, the fiber-optic link is configured for normal operation.

Loopback activation or deactivation has the same effect as plugging in or unplugging the fiber-optic cable. The Link OK status bit will transition from "1" to "0". Recovery time is required for the optical transceiver module and transceiver chip. Upon loopback activation or deactivation, poll the Link OK status bit for 1.5 seconds. During this interval, the Link OK status bit should transition from "0" to "1". It is likely that a fiber-optic interface data error will be detected and logged in the status registers. After loopback is activated, write or read transactions to the remote RAM window may occur. The appropriate mapping register must be initialized as active. The initialization procedure in section 5.2 should follow loopback deactivation. Local deactivation / remote activation or remote deactivation / local activation should not be combined in a single register transaction.

# Chapter 4: The PCI Adapter Card

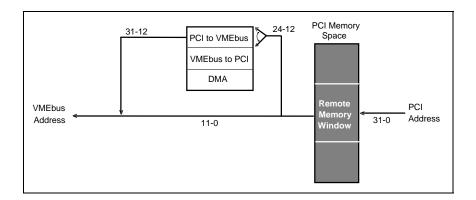

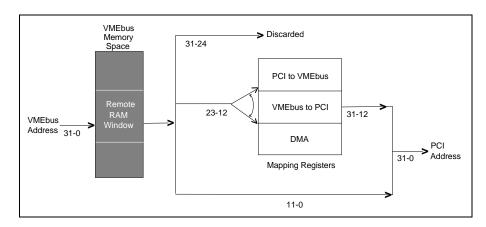

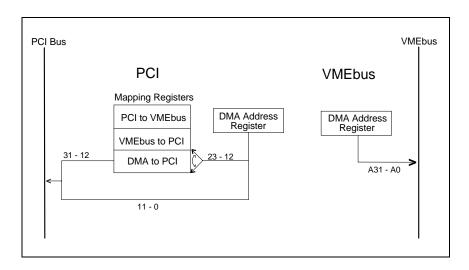

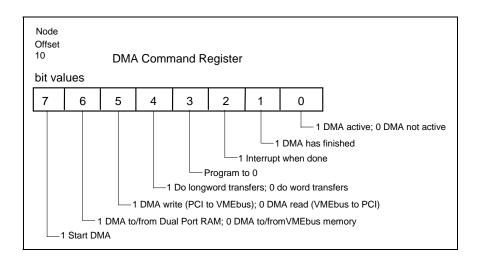

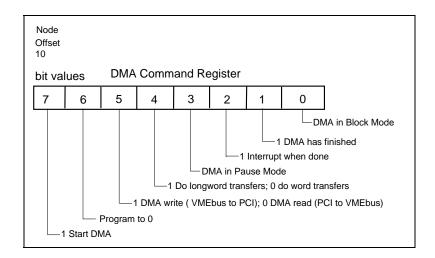

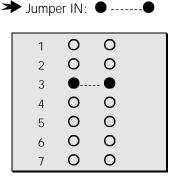

### 4.0 Introduction