Gamma Ray Energy Tracking In-Beam Nuclear Array

# **GRETINA Digitizer Specification**

Document # GRT-3-060815-0

March 25, 2008

Dionisio Doering, John Joseph, Harold Yaver, Sergio Zimmermann

# Accepted and Approved by:

| Sergio Zimmermann | Date |

|-------------------|------|

|-------------------|------|

| I-Yang Lee Date |  |

|-----------------|--|

|-----------------|--|

## GRETINA Digitizer Specification Gamma Ray Energy Tracking In-Beam Nuclear Array (GRETINA)

# **Revision History**

| Revision No. | Pages Affected                             | Effective Date |

|--------------|--------------------------------------------|----------------|

| 0            | First Release                              | 9/6/2006       |

| 1            | 10, 11, 12, 13, 26, 27, 28, 29, 33, 34, 35 |                |

| 2            | 5, 17, 19, 27                              | 3/25/2008      |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

|              |                                            |                |

| 1 | INTRODUCTION                                           | 5  |

|---|--------------------------------------------------------|----|

|   | 1.1 OVERALL DESCRIPTION                                | 5  |

|   | 1.2 PRECEDENCE                                         | 5  |

| 2 | DIGITIZER MODULES                                      | 5  |

|   | 2.1 GRETINA DIGITIZER TOP LEVEL BLOCK DIAGRAM          | 5  |

|   | 2.2 FUNCTIONAL BLOCKs                                  | 6  |

|   | 2.2.1 VMEBUS INTERFACE                                 | 6  |

|   | 2.2.1.1 VME INTERFACE DESCRIPTION                      | 7  |

|   | 2.2.1.2 VME TO MAIN FPGA TIMING                        | 8  |

|   | 2.2.1.3 GRETINA DIGITIZER MEMORY MAP                   | 10 |

|   | 2.2.1.4 VME FPGA MEMORY MAP                            | 10 |

|   | 2.2.1.5 FLASH MEMORY FOR MAIN FPGA CONFIGURATION       | 11 |

|   | 2.2.1.6 VMEBUS J1/P1 CONNECTOR PIN ASSIGNMENTS         | 14 |

|   | 2.2.1.7 VMEBUS J2/P2 CONNECTOR PIN ASSIGNMENTS         | 16 |

|   | 2.2.2 FRONT END PREAMP AND DIGITIZER                   | 17 |

|   | 2.2.2.1 ANALOG INPUT                                   | 17 |

|   | 2.2.2.2 FRONT END PREAMP                               |    |

|   | 2.2.2.3 CENTRAL CONTACT REPEATER OUTPUT                | 20 |

|   | 2.2.2.4 DIGITIZER CIRCUIT                              | 20 |

|   | 2.2.3 EVENT FIFO                                       | 20 |

|   | 2.2.4 MAIN FPGA                                        |    |

|   | 2.2.4.1 MODES OF OPERATION                             | 22 |

|   | 2.2.4.1.1 INTERNAL MODE                                | 23 |

|   | 2.2.4.1.2 EXTERNAL MODE                                | 23 |

|   | 2.2.4.1.3 INTERNAL WITH VALIDATION MODE                | 23 |

|   | 2.2.4.1.4 TRIGGER TIMING & CONTROL LINK MODE           |    |

|   | 2.2.4.2 CHECKING SYNCHRONISM                           | 24 |

|   | 2.2.4.3 INITIALIZATION                                 |    |

|   | 2.2.4.3.1 SYSTEM INITIALIZATION                        |    |

|   | 2.2.4.3.2 TRIGGER TIMING & CONTROL LINK INITIALIZATION | 25 |

|   | 2.2.4.4 CLOCK MANAGEMENT                               | 25 |

|   | 2.2.4.5 FIFO AND OUTPUT DATA FORMAT                    | 26 |

|   | 2.2.4.6 MAIN FPGA REGISTERS                            | 28 |

|   | 2.2.5 DAC OUTPUT                                       |    |

|   | 2.2.6 FRONTBUS INTERFACE                               |    |

|   | 2.2.6.1 FRONT BUS REGISTERS                            |    |

|   | 2.2.7 SERIALIZER/DESERIALIZER INTERFACE                | 48 |

|   | 2.2.8 AUXILIARY INPUT INTERFACE                        |    |

|   | 2.2.9 100MHz CLOCK DISTRIBUTION                        |    |

|   | 2.2.10 FRONT PANEL INDICATORS                          |    |

|   | 2.2.11 VOLTAGE MONITORS                                |    |

|   | 2.2.12 TEMPERATURE MONITORS                            |    |

|   | 2.2.13 POWER REQUIREMENTS                              |    |

| 3 |                                                        |    |

|   | 3.1 COMPONENT PLACEMENT                                |    |

| 4 | REFERENCES                                             | 53 |

#### 1 INTRODUCTION

#### 1.1 OVERALL DESCRIPTION

The GRETINA Digitizer module is a combination of digitizer and digital signal processor. It accepts 10 inputs directly from the detector module pre-amplifiers and digitizes at a nominal frequency of 100 MHz with 14 bits ADC precision. The ADC counts interface to the FPGA, which digitally processes the data.

#### **1.2 PRECEDENCE**

The design of the GRETINA Digitizer electronics board must meet the Digitizer specific requirements defined in the GRETINA Electronics Requirements Document.

#### 2 **DIGITIZER MODULES**

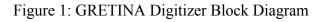

#### **GRETINA DIGITIZER BLOCK DIAGRAM** FRONT PANEL **INDICATORS 100MHz CLOCK DIST** CENTRAL CONTACT OUT EVENT ٨ FIFO VME **CH9 FE/ADC** CTRL **MAIN FPGA** (1MB) & CH8 FE/ADC XC3S5000-5FG900 I/O (633 USER I/O) CH0 FE/ADC DAC OUT **EXT CLOCK IN SER/DES IO 50MHz REF CLK** 50MHz RCLK CONTROL FRONTBUS IO 3:1 MUX **AUX IO (11)**

### 2.1 GRETINA DIGITIZER TOP LEVEL BLOCK DIAGRAM

#### 2.2 FUNCTIONAL BLOCKS

The LBNL GRETINA Digitizer Electronics board will include all of the functions and blocks described in the following sections and listed below.

VMEBUS INTERFACE Interface to the Host Computer System

FRONT END PREAMP AND DIGITIZER Interface to the FE Pre Amplifiers of the Crystal Detectors

EVENT FIFO 256K x 32 FIFO used to buffer Event Data while the VME Host is fetching hit data

MAIN FPGA Real-Time FPGA Signal Processor

DAC OUTPUT General Purpose Current or Voltage output

FRONTBUS INTERFACE Interface used by all Digitizers in one crate to communicate and share vital information

SERIALIZER/DESERIALIZER Interface to the Trigger and Timing System

AUXILIARY INPUT INTERFACE 16 General Purpose TTL Inputs to the MAIN FPGA

100MHz CLOCK DISTRIBUTION Onboard Clock Management

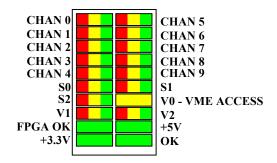

FRONT PANEL INDICATORS User defined Front Panel Monitoring

VOLTAGE MONITORS Monitoring of voltage level of all key power supply voltages

TEMPERATURE MONITORS Simple over-temperature switches

#### 2.2.1 VMEBUS INTERFACE

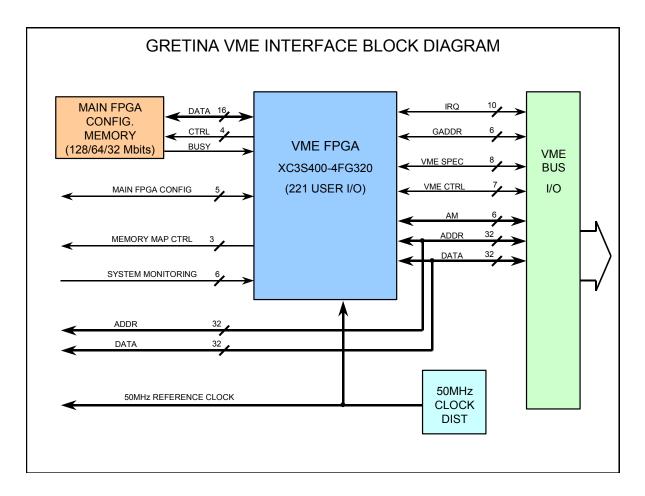

The GRETINA Digitizer board will communicate with a host computer using the VME64x protocol. The slave interface will support the A32/D32 address and data format for block transfers and single read/write access. Geographical addressing (GADDR) will be used to determine the base address of each board in a crate, so any Digitizer can be used in any slot without the need to set a board address on the electronics card. The block diagram of the VME Interface is shown in Figure 2.

Figure 2: GRETINA VME Interface Block Digram

## 2.2.1.1 VME INTERFACE DESCRIPTION

The design of the VME interface on the GRETINA Digitizer will be implemented using a Xilinx Spartan3 FPGA and a small number of buffers, drivers and transceivers that are required to physically interface to the VME back plane. The VME FPGA will control the block transfer and programmed IO read/write access to the Digitizer Main FPGA, the configuration Flash memory, and the VME FPGA internal register memory map. The VME FPGA will include functional blocks that will control reset and configuration of the Main FPGA at system power-on and on command when requested by the VME host. The 3 main addressable locations on the Digitizer board are the Main FPGA, the VME Controller FPGA, and the Main FPGA Configuration Memory. Control of the on-board peripherals will be provided through the Main FPGA memory map. These peripherals include the Front End ADC circuits, the output DACs, the FrontBus interface, and the Main Readout FIFO to list a few.

The VME interface requires a stand-alone 50MHz clock that will be buffered through a 1 to 4 low skew differential clock distribution circuit. The 50MHz clock signal will be routed to the Main FPGA and to the Serializer/Deserializer (SER/DES) block to satisfy the operational requirements of each sub-system. Because the SER/DES requires a clean

stable clock, the oscillator component of the distribution shall be a 50.000MHz SMT Temperature Compensated Crystal Oscillator (TCXO) with better than +/-5.0 ppm overall frequency tolerance. A constant clock is required by the Main FPGA to allow readout of internal status registers in the case that the recovered SER/DES clock falls out of lock or is not present.

The configuration memory will be implemented with one Intel 128/64/32Mbit, 128k sector flash memory component and will be used primarily to hold configuration programs for the Main FPGA. The Main FPGA Configuration Flash will be accessible on the VME bus for Read/Write operations as required.

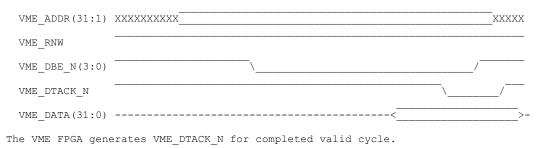

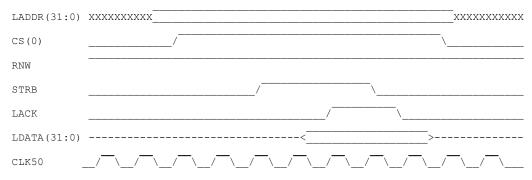

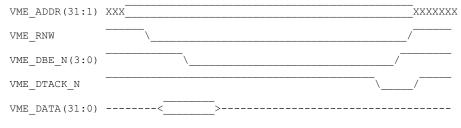

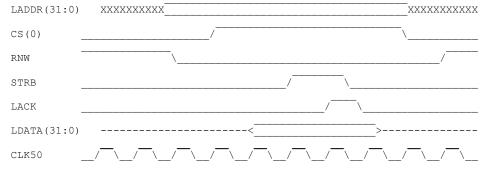

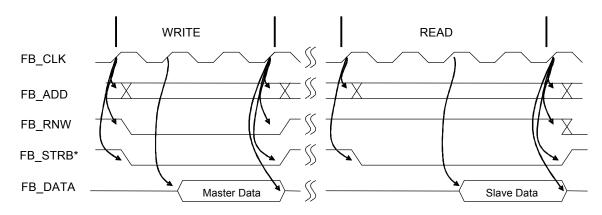

#### 2.2.1.2 VME TO MAIN FPGA TIMING

The VMEBus side of the Host to Digitizer Interface is an asynchronous interface that is controlled by any Industry Standard VME Crate Master. The VME FPGA on the Digitizer is configured to resynchronize the data transfers to and from the VME Crate Master. The interface between the VME FPGA and the Main FPGA on the Digitizer board is a synchronous interface, and all control and data signals are generated and sampled on the rising edge of the on-board 50MHz clock.

The following timing diagrams show representations of programmed I/O (single data transfer) access only. Block transfer is supported for all registers in the MAIN and VME FPGA. The Block Transfer timing for transfers from the MAIN FPGA to the VME FPGA is not shown because the VME FPGA will handle all the control protocol as long as the MAIN FPGA asserts LACK for every valid DATA STROBE/CYCLE. Block Transfer will be allowed for read access to the MAIN FPGA configuration Flash memory. Block Transfer for write access to the MAIN FPGA configuration Flash memory may not be supported.

#### Local VME Read Cycle

The MAIN FPGA generates LACK when LDATA is valid on the data bus.

#### Local VME Write Cycle

The VME FPGA generates VME\_DTACK N for completed valid cycle.

#### VME to MAIN Write Timing

The MAIN FPGA generates LACK when LDATA is latched in the device.

## 2.2.1.3 GRETINA DIGITIZER MEMORY MAP

The Geographical Address bits on the VME back plane determine the Base Address of the Digitizer boards. The GA bits are compared to bits 24 to 20 of the VME address word.

|         |      | GRETIN  | A Digitizer: Top Level Memory Map (CL Proposal)     |

|---------|------|---------|-----------------------------------------------------|

| (31:25) | (24) | (23:20) | (19:0) Start Address/Description - D32 unless noted |

| OS Dep  | GA4  | GA3:GA0 |                                                     |

| 0x0     | 0    | SLOT    | 0x00000: Main FPGA Registers                        |

| 0x0     | 0    | SLOT    | 0x00900: VME FPGA Registers                         |

| 0x0     | 0    | SLOT    | 0x00980: Flash Address                              |

| 0x0     | 0    | SLOT    | 0x00984: Flash Data with Address Auto-Increment     |

| 0x0     | 0    | SLOT    | 0x00988: Flash Data                                 |

| 0x0     | 0    | SLOT    | 0x0098C: Flash Commands (16 bit)                    |

| 0x0     | 0    | SLOT    | 0x01000: Read Out FIFO Access                       |

| 0x0     | 0    | SLOT    | 0x80FFC: Top of Read Out FIFO                       |

Table 1 – GRETINA Digitizer Memory Map

#### 2.2.1.4 VME FPGA MEMORY MAP

| Description                                                                                                                                                                 | Address                  | Access                  | Width |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------|-------|

| DIGITIZER MAIN FPGA Configuration Control Register                                                                                                                          | BASE_ADDRESS<br>+ 0x0900 | RW                      | 32    |

| All bits in the Register are Self-Clearing, unless noted other                                                                                                              | wigo                     | Bit Value               |       |

| All bits in the Register are self-creating, unless noted other                                                                                                              | wise.                    | 1                       | 0     |

| <b>Bit 0:</b> Configure Main Digitizer FPGA<br>If this bit is set, the Main Digitizer FPGA will be erased<br>with a Configuration Bit Stream that is stored in the on board |                          | Configure<br>Main FPGA  | Idle  |

| <b>Bit 1:</b> Configure Main Digitizer FPGA<br>If this bit is set, the Main Digitizer FPGA will be erased<br>with a Configuration Bit Stream that is stored in the on board |                          | Configure<br>Diags FPGA | Idle  |

| Bit 2: TBD                                                                                                                                                                  |                          |                         |       |

| Bit 3: TBD                                                                                                                                                                  |                          |                         |       |

| Bit 4: Reset Main Digitizer FPGA<br>If this bit is set, a reset pulse is sent to the Main Digitize                                                                          | r FPGA                   | Reset                   | Idle  |

| Bit 5: Reset Flash Memory<br>If this bit is set, a reset pulse is sent the Flash Memory                                                                                     |                          | Reset                   | Idle  |

| Bit 6: TBD                                                                                                                                                                  |                          |                         |       |

| Bit 7: TBD                                                                                                                                                                  |                          |                         |       |

| <b>Bit 8:</b> Configuration Override<br>If this bit is set, the FPGA will not send configuration da<br>FPGA when a configuration command is issued                          | ta to the Main           | Override                | Idle  |

| Bits[31:6]: TBD                                                                                                                                                             |                          |                         |       |

| Description                                       | Address                  | Access    | Width  |

|---------------------------------------------------|--------------------------|-----------|--------|

| DIGITIZER MAIN FPGA Configuration Status Register | BASE_ADDRESS<br>+ 0x0904 | R         | 32     |

| Status of the MAIN FPGA Configuration             |                          | Bit Value |        |

| Status of the MAIN FPGA Configuration             |                          | 1         | 0      |

| Bit 0: MAIN FPGA DONE Bit Status                  |                          | DONE      | CNFG   |

| Bit 1: MAIN FPGA INIT_N Bit Status                |                          | ERASE     | OK     |

| Bit 2: MAIN FPGA PROG N Bit Status                |                          | CNFG      | OK     |

| Bit 3: MAIN FPGA HALT Configuration Status        |                          | HALT      | OK     |

| Bit 4: MAIN FPGA RESET Status                     |                          | RESET     | OK     |

| Bit 5: MAIN FPGA Configuration Enable Status      |                          | Config    | OK     |

| Bit 6: MAIN FPGA Configuration Done Status        |                          | Done      | OK     |

| Bit 7: Flash Memory Status                        |                          | Busy      | Ready  |

| Bit 8: Main FPGA DMM LACK                         |                          | ACK       | IDLE   |

| Bit 9: VME FPGA DCM PS Done                       |                          | Done      |        |

| Bit 10: VME FPGA DCM Locked                       |                          | Lock      | Unlock |

| Bits[31:11]: TBD                                  |                          |           |        |

| Description                                       | Address                  | Access    | Width |

|---------------------------------------------------|--------------------------|-----------|-------|

| DIGITIZER Voltage and Temperature Status Register | BASE_ADDRESS<br>+ 0x0908 | R         | 32    |

| Status of the Digitizer Voltage and Temperature   |                          | Bit Value |       |

| Status of the Digitizer voltage and temperature   |                          | 1         | 0     |

| Bit 0: All Power Supplies Status                  |                          | FAULT     | OK    |

| Bit 1: Over Voltage Status                        |                          | FAULT     | OK    |

| Bit 2: Under Voltage Status                       |                          | FAULT     | OK    |

| Bit 3: Temperature Sensor 0 Status                |                          | FAULT     | OK    |

| Bit 4: Temperature Sensor 1 Status                |                          | FAULT     | OK    |

| Bit 5: Temperature Sensor 2 Status                |                          | FAULT     | OK    |

| Bits[31:6]: Not Used                              |                          |           |       |

| Description                           | Address                  | Access     | Width        |

|---------------------------------------|--------------------------|------------|--------------|

| VME GP CONTROL Register               | BASE_ADDRESS<br>+ 0x0910 | RW         | 32           |

| General purpose VME Control setting   |                          | Bit Value  |              |

| General pulpose VME control setting   |                          | 1          | 0            |

| Bit [0]: Clock Select 0               |                          | EXT/REF    | SD CLK       |

| Bit [1]: Clock Select 1               |                          | EXT CLK    | REF CLK      |

| Bit [3:2]: TBD                        |                          | EXT CLK    | REF CLK      |

| Bit [4]: Set FLASH in PROG/ERASE MODE |                          | PROG/ERASE | READ<br>ONLY |

| Bits [31:2]: TBD                      |                          | VALU       | Ξ            |

| Description                                 | Address                  | Access    | Width |

|---------------------------------------------|--------------------------|-----------|-------|

| VME TIMEOUT VALUE Register                  | BASE_ADDRESS<br>+ 0x0914 | RW        | 32    |

| VME timeout counter value, 20ns increments  |                          | Bit Value |       |

| VME climeout councer value, zons increments |                          | 1         | 0     |

| Bits [31:0]: VME TimeOut Value              |                          | VALU      | E     |

| Description                               | Address                  | Access | Width |

|-------------------------------------------|--------------------------|--------|-------|

| VME FPGA VERSION/REVISION Status Register | BASE_ADDRESS<br>+ 0x0920 | R      | 32    |

|                                           |                          | Bit Va | lue   |

|                                           |                          | 1      | 0     |

| Bits [15: 0]: Serial Number (11:0)        |                          | VALUE  |       |

| Bits [23:16]: BOARD Revision Number       |                          | VALUE  |       |

| Bits [31:24]: VHDL Version Number         |                          | VALUE  |       |

| Description                                            | Address                            | Access    | Width |

|--------------------------------------------------------|------------------------------------|-----------|-------|

| VME FPGA SAND BOX REGISTER BLOCK                       | BASE_ADDRESS<br>+ 0x0930 to 0x093C | RW        | 32    |

| A Desistence to use for most and Debug                 |                                    | Bit Value |       |

| 4 Registers to use for Test and Debug                  |                                    | 1         | 0     |

| Bits [31: 0]: Registers for general purpose Read/Write | 300088                             | VALU      | F     |

#### 2.2.1.5 FLASH MEMORY FOR MAIN FPGA CONFIGURATION

The Main FPGA configuration data is stored in a 128Mbit Intel Flash memory IC that can be accessed over the VME bus. The data bus on the device is 16 bits wide, so the VME FPGA translates the D32 access to the proper byte locations automatically. The Flash memory has 128 128k Bytes blocks and supports 32 Bytes of block transfer programming in an internal write buffer. Because the Flash commands require single access 16 bit writes, the commands occupy a different address map range than the data locations. The Main FPGA configuration data starts at address 0x0, or block 0 of the flash.

The flash access is performed using a Host-Port-Interface type of architecture that is controlled using 4 registers in the VME Interface FPGA. The Flash Address Register is used to store the memory location that is required for each specific operation. If the Flash is accessed using the Flash Data Register with Address Auto-Increment, then the

address held in the value of the flash address will be incremented by 4 at the end of each cycle. Data access through the standard Flash Data Register leaves the address value static. Command access through the Flash Command Register writes 16 bit commands to the address location in the address register.

At power up, the flash is in "Read Array" mode, but after and Erase or command, a "Read Array" command must be sent to reset the internal state machine. The "Read Array" command is a write of data 0xFFh to the Flash Command Register in the VME FPGA. A Flash memory reset will also put the device back in "Read Array" mode.

To perform a block-erase operation, a Block Erase command sequence must be issued at the desired block address. The Block Erase command sequence requires two cycles, and is shown in the table below:

| Command                     | VME     | VME Data                        |

|-----------------------------|---------|---------------------------------|

|                             | Address |                                 |

| Write – Sector Address      | 0x0980  | Base Address of sector to erase |

| Write - Setup Block Erase   | 0x098C  | 0x0020h                         |

| Write – Confirm Block Erase | 0x098C  | 0x00D0h                         |

| Read - Status Signal        | 0x0904  | Bit(7)                          |

If Bit(7) = 0, then Block Erase is complete

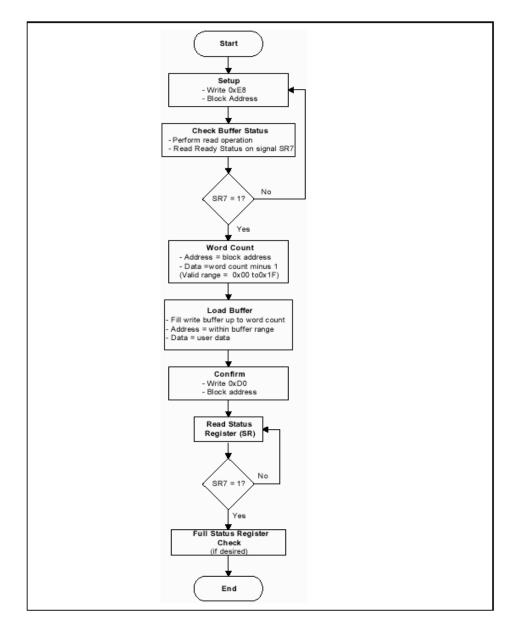

Buffered programming operations simultaneous program multiple words into the flash memory array, significantly reducing effective word-write times. User-data is first written to a write buffer, and then programmed into the flash memory array in buffer-size increments. Optimal performance and power consumption is realized only by aligning the start address on 32-word boundaries. Crossing a 32-word boundary during a buffered programming operation can cause programming time to double.

To perform a buffered programming operation, first issue the Buffered Program setup command at the desired starting address. Status Register Polling SR7 determines writebuffer availability (0 = not available, 1 = available). If the write buffer is not available, re-issue the setup command and check SR7; repeat until SR7 = 1. The Status Signal output can also be checked to indicate if the Flash is busy or ready. Next, issue the word count at the desired starting address. The word count represents the total number of words to be written into the write buffer, minus one. This value can range from 0x01h (2 bytes) to a maximum of 0x1Fh (32 bytes). If the part is configured in 16 bit mode, the maximum value is 0xFh. Following the word count, the write buffer is filled with user-data. User-data is programmed into the flash array at the address issued when filling the write buffer. After all user-data is written into the write buffer, issue the confirm command. If a command other than the confirm command is issued to the device, a command sequence error occurs and the operation aborts. After issuing the confirm command, write-buffer contents are programmed into the flash memory array. The Status Signal indicates a busy status (Bit7 = 1) during array programming. Issuing another setup command, and repeating the buffered programming bus-cycle sequence can initiate additional buffered programming operations. However, any errors in the Status Register must first be cleared before another buffered programming operation can be initiated. (See Ref [4] for more specification details).

| Command                       | Address | Data               |

|-------------------------------|---------|--------------------|

| Write – Program start address | 0x0980  | Start address      |

| Write - Setup Write Buffer    | 0x098C  | 0x00E8h            |

| Read - Status Signal          | 0x0904  | Bit(7)             |

| Write – Word Count            | 0x098C  | 0x0001h to 0x000Fh |

| Write – Load Buffer           | 0x0984  | Array Data         |

| Write – Confirm Write         | 0x098C  | 0x00D0h            |

| Read - Status Signal          | 0x0904  | Bit (7)            |

If Bit(7) = 0, then Buffer Write is complete

Figure 3: Flash Write to Buffer Flow Chart

#### 2.2.1.6 VMEBUS J1/P1 CONNECTOR PIN ASSIGNMENTS

A 160-pin connector will be used for P1/J1 to allow use of the Geographical addressing pins, the 3.3V power supply, and extra Ground pins available in the standard VME64x crate. The VME Interface on the Digitizer is a simple Slave type interface and will not use any of the Bus Grant or Bus Request capabilities available on the P1 connector. The VMEBus SYSCLK pin will not be connected on the Digitizer board because the on-board system require clocks with stability in the range of +/5 ppm. All signals shaded in red in Table 2 are not connected to the Digitizer VME Interface.

|     |        | VME I/O: J1/P1 P | in Assignments (VI | ME64x)    |        |

|-----|--------|------------------|--------------------|-----------|--------|

| Pin | Row Z  | Row A            | Row B              | Row C     | Row D  |

| 1   | MPR    | D00              | BBSYn              | D08       | VPC    |

| 2   | GND    | D01              | BCLRn              | D09       | GND    |

| 3   | MCLK   | D02              | ACFAILn            | D10       | +V1    |

| 4   | GND    | D03              | BG0INn             | D11       | +V2    |

| 5   | MSD    | D04              | <b>BG0OUTn</b>     | D12       | RsvU   |

| 6   | GND    | D05              | BG1INn             | D13       | -V1    |

| 7   | MMD    | D06              | <b>BG1OUTn</b>     | D14       | -V2    |

| 8   | GND    | D07              | BG2INn             | D15       | RsvU   |

| 9   | MCTL   | GND              | BG2OUTn            | GND       | GAPn   |

| 10  | GND    | SYSCLK           | BG3INn             | SYSFAILn  | GA0n   |

| 11  | RESPn  | GND              | BG3OUTn            | BERRn     | GA1n   |

| 12  | GND    | DS1n             | BR0n               | SYSRESETn | +3.3V  |

| 13  | RsvBus | DS0n             | BR1n               | LWORDn    | GA2n   |

| 14  | GND    | WRITEn           | BR2                | AM5       | +3.3V  |

| 15  | RsvBus | GND              | BR3n               | A23       | GA3n   |

| 16  | GND    | DTACKn           | AM0                | A22       | +3.3V  |

| 17  | RsvBus | GND              | AM1                | A21       | GA4n   |

| 18  | GND    | Asn              | AM2                | A20       | +3.3V  |

| 19  | RsvBus | GND              | AM3                | A19       | RsvBus |

| 20  | GND    | IACKn            | GND                | A18       | +3.3V  |

| 21  | RsvBus | IACKINn          | SERA               | A17       | RsvBus |

| 22  | GND    | IACKOUTn         | SERB               | A16       | +3.3V  |

| 23  | RsvBus | AM4              | GND                | A15       | RsvBus |

| 24  | GND    | A01              | IRQ7n              | A14       | +3.3V  |

| 25  | RsvBus | A02              | IRQ6n              | A13       | RsvBus |

| 26  | GND    | A03              | IRQ5n              | A12       | +3.3V  |

| 27  | RsvBus | A04              | IRQ4n              | A11       | LI/In  |

| 28  | GND    | A05              | IRQ3n              | A10       | +3.3V  |

| 29  | RsvBus | A06              | IRQ2n              | A09       | LI/On  |

| 30  | GND    | A07              | IRQ1n              | A08       | +3.3V  |

| 31  | RsvBus | -12 VDC          | +5 VSTDBY          | +12 VDC   | GND    |

| 32  | GND    | +5 VDC           | +5 VDC             | +5 VDC    | VPC    |

Table 2 – VME P1 Signals

#### 2.2.1.7 VMEBUS J2/P2 CONNECTOR PIN ASSIGNMENTS

A 96 pin connector will be used for P2/J2 because there are no proposed connections to Row D and Row Z.

|     | VME I/O: P2/J2 Pin Assignments (VME64x) |        |        |        |         |  |  |

|-----|-----------------------------------------|--------|--------|--------|---------|--|--|

| Pin | Row Z                                   | Row A  | Row B  | Row C  | Row D   |  |  |

| 1   | UsrDef                                  | UsrDef | +5 VDC | UsrDef | GND     |  |  |

| 2   | GND                                     | UsrDef | GND    | UsrDef | Aux Bus |  |  |

| 3   | UsrDef                                  | UsrDef | RETRYn | UsrDef | Aux Bus |  |  |

| 4   | GND                                     | UsrDef | A24    | UsrDef | Aux Bus |  |  |

| 5   | UsrDef                                  | UsrDef | A25    | UsrDef | Aux Bus |  |  |

| 6   | GND                                     | UsrDef | A26    | UsrDef | Aux Bus |  |  |

| 7   | UsrDef                                  | UsrDef | A27    | UsrDef | Aux Bus |  |  |

| 8   | GND                                     | UsrDef | A28    | UsrDef | Aux Bus |  |  |

| 9   | UsrDef                                  | UsrDef | A29    | UsrDef | Aux Bus |  |  |

| 10  | GND                                     | UsrDef | A30    | UsrDef | GND     |  |  |

| 11  | UsrDef                                  | UsrDef | A31    | UsrDef | Aux Bus |  |  |

| 12  | GND                                     | UsrDef | GND    | UsrDef | Aux Bus |  |  |

| 13  | UsrDef                                  | UsrDef | +5 VDC | UsrDef | Aux Bus |  |  |

| 14  | GND                                     | UsrDef | D16    | UsrDef | Aux Bus |  |  |

| 15  | UsrDef                                  | UsrDef | D17    | UsrDef | Aux Bus |  |  |

| 16  | GND                                     | UsrDef | D18    | UsrDef | Aux Bus |  |  |

| 17  | UsrDef                                  | UsrDef | D19    | UsrDef | Aux Bus |  |  |

| 18  | GND                                     | UsrDef | D20    | UsrDef | Aux Bus |  |  |

| 19  | UsrDef                                  | UsrDef | D21    | UsrDef | GND     |  |  |

| 20  | GND                                     | UsrDef | D22    | UsrDef | Aux Bus |  |  |

| 21  | UsrDef                                  | UsrDef | D23    | UsrDef | Aux Bus |  |  |

| 22  | GND                                     | UsrDef | GND    | UsrDef | Aux Bus |  |  |

| 23  | UsrDef                                  | UsrDef | D24    | UsrDef | Aux Bus |  |  |

| 24  | GND                                     | UsrDef | D25    | UsrDef | Aux Bus |  |  |

| 25  | UsrDef                                  | UsrDef | D26    | UsrDef | GND     |  |  |

| 26  | GND                                     | UsrDef | D27    | UsrDef | Aux Bus |  |  |

| 27  | UsrDef                                  | UsrDef | D28    | UsrDef | Aux Bus |  |  |

| 28  | GND                                     | UsrDef | D29    | UsrDef | Aux Bus |  |  |

| 29  | UsrDef                                  | UsrDef | D30    | UsrDef | UsrDef  |  |  |

| 30  | GND                                     | UsrDef | D31    | UsrDef | UsrDef  |  |  |

| 31  | UsrDef                                  | UsrDef | GND    | UsrDef | GND     |  |  |

| 32  | GND                                     | UsrDef | +5 VDC | UsrDef | VPC     |  |  |

Table 3 - VME P2 Signals

#### 2.2.2 FRONT END PREAMP AND DIGITIZER

Each GRETINA Digitizer electronics board has 10 front-end input channels. The data signals from the detector amplifiers are transmitted to the digitizer front-end inputs on differential wire pairs in a mass terminated cable assembly. The receptacle connector on the Digitizer is a 100-pin double density D type with 75-mil contact spacing, manufactured by ITT/Cannon, part number 2DD100SBRP. The received input signal is buffered with a true differential input amplifier before the signal is digitized using a 14-bit 100Msps Analog to Digital Converter. The digitized data of all channels is read out simultaneously by a controller/processor FPGA at 200Mbytes/sec/channel.

#### 2.2.2.1 ANALOG INPUT

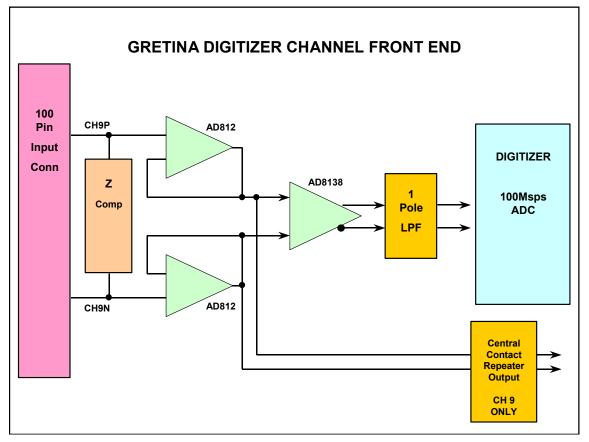

The analog inputs to the digitizer front-end amplifiers are true differential, high impedance type. A block diagram is shown in Figure 4.

Figure 4: Digitizer Front End

The pin assignments for the analog input signals are defined in Table 4. The labeling for the signals is as follows:

CH0P: Channel 0, positive polarity input signal CH0N: Channel 0, negative polarity input signal SHIELD0: Internal cable shield for Channel 0 wire pair

CH1P: Channel 1, positive polarity input signal CH1N: Channel 1, negative polarity input signal SHIELD1: Internal cable shield for Channel 1 wire pair

. . . . . . . . .

CH8P: Channel 8, positive polarity input signal CH8N: Channel 8, negative polarity input signal SHIELD8: Internal cable shield for Channel 8 wire pair

CH9P: Channel 9, positive polarity input signal CH9N: Channel 9, negative polarity input signal SHIELD9: Internal cable shield for Channel 9 wire pair

SP1: Auxiliary wire pair connections and shield SP2: Auxiliary wire pair connections and shield

GND: Board Ground

| (1  | Digitizer Input Interface<br>(100pin ITT Cannon Double Density D Connector, 2DD100SBRP) |     |             |     |             |           |             |

|-----|-----------------------------------------------------------------------------------------|-----|-------------|-----|-------------|-----------|-------------|

|     | Mating Connector: 2DD100P                                                               |     |             |     |             |           |             |

| Pin | Description                                                                             | Pin | Description | Pin | Description | Pin       | Description |

| 1   | SHIELD9                                                                                 | 27  | SHIELD9     |     |             |           |             |

| 2   | CH9N                                                                                    | 28  | CH9P        | 52  | SP2         | 76        | SP2         |

| 3   | GND                                                                                     | 29  | GND         | 53  | GND         | 77        | SP2         |

| 4   | GND                                                                                     | 30  | GND         | 54  | SHIELD8     | <b>78</b> | SHIELD8     |

| 5   | GND                                                                                     | 31  | GND         | 55  | CH8P        | 79        | CH8N        |

| 6   | SHIELD7                                                                                 | 32  | SHIELD7     | 56  | GND         | 80        | GND         |

| 7   | CH7N                                                                                    | 33  | CH7P        | 57  | GND         | 81        | GND         |

| 8   | GND                                                                                     | 34  | GND         | 58  | GND         | 82        | GND         |

| 9   | GND                                                                                     | 35  | GND         | 59  | SHIELD6     | 83        | SHIELD6     |

| 10  | GND                                                                                     | 36  | GND         | 60  | CH6P        | 84        | CH6N        |

| 11  | SHIELD5                                                                                 | 37  | SHIELD5     | 61  | GND         | 85        | GND         |

| 12  | CH5N                                                                                    | 38  | CH5P        | 62  | GND         | 86        | GND         |

| 13  | GND                                                                                     | 39  | GND         | 63  | GND         | 87        | GND         |

| 14  | GND                                                                                     | 40  | GND         | 64  | SHIELD4     | 88        | SHIELD4     |

| 15  | GND                                                                                     | 41  | GND         | 65  | CH4P        | 89        | CH4N        |

| 16  | SHIELD3                                                                                 | 42  | SHIELD3     | 66  | GND         | 90        | GND         |

| 17  | CH3N                                                                                    | 43  | CH3P        | 67  | GND         | 91        | GND         |

| 18  | GND                                                                                     | 44  | GND         | 68  | GND         | 92        | GND         |

| 19  | GND                                                                                     | 45  | GND         | 69  | SHIELD2     | 93        | SHIELD2     |

| 20  | GND                                                                                     | 46  | GND         | 70  | CH2P        | 94        | CH2N        |

| 21  | SHIELD1                                                                                 | 47  | SHIELD1     | 71  | GND         | 95        | GND         |

| 22  | CH1N                                                                                    | 48  | CH1P        | 72  | GND         | 96        | GND         |

| 23  | GND                                                                                     | 49  | GND         | 73  | GND         | 97        | GND         |

| 24  | GND                                                                                     | 50  | GND         | 74  | SHIELD0     | 98        | SHIELD0     |

| 25  | SP1                                                                                     | 51  | SP1         | 75  | CHOP        | 99        | CH0N        |

| 26  | SP1                                                                                     |     |             |     |             | 100       | GND         |

#### Table 4 - Digitizer Input Pin Assignments

#### 2.2.2.2 FRONT END PREAMP

High impedance input buffers are used to allow the cable termination resistors to dominate the impedance matching of the transmission line and to improve isolation while allowing signal balance on the wire pair. The full-scale amplitude at the input of the front-end amplifier is 10MeV for the central contact signal and 30MeV for all of the segment signals.

#### 2.2.2.3 CENTRAL CONTACT REPEATER OUTPUT

The central contact of the detector shall be connected to the Channel 9 wire pair of the Master Digitizer that is connected to a differential repeater amplifier as shown in Figure 4. The repeater amplifier is used to buffer the Central Contact signal for connection to a front panel LEMO connector. This allows the Central Contact signal to be viewed externally during run-time.

#### 2.2.2.4 DIGITIZER CIRCUIT

The Digitizer circuit will utilize a 100Msps Analog Devices AD6645ASQ-105 ADC for each input channel. There is a one-pole anti-aliasing filter at the input of the ADC that can be loaded if required. The Main FPGA reads out each digitizer channel ADC simultaneously and writes the data to an internal circular buffer in real time.

#### 2.2.3 EVENT FIFO

The main FPGA writes full events into the event FIFO after receiving a valid command from the trigger system. The event FIFO is implemented using two 256Kx18, 7ns FIFO memory chips. Write control is managed solely by the main FPGA while read control is managed by the main FPGA through the VME interface. The Event FIFO shall be write and read accessible by the VME host to allow functional testing of the FIFO components.

#### 2.2.4 MAIN FPGA

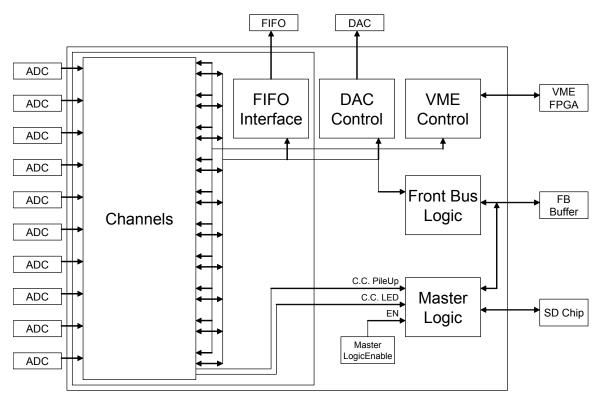

Figure 1 shows the block diagram of the Digitizer. The main FPGA is responsible for control the data acquisition. It uses a Spartan 3 FPGA XC3S5000 (5M gates, 104 Block RAMs) from Xilinx. The configuration memory has a minimum of 16 Mbits and is accessible from VME for in system reconfiguration. The Main FPGA is configured in Slave-Serial Mode as described in the Xilinx Spartan 3 data sheets.

Four Digitizers instrument one crystal. One of these modules is configured as master and is connected to the crystal's central contact. The other three modules are configured as slaves. The VHDL code for all the 4 modules will be identical which means that we are going to have one part of the code that is the master and another part that is the slave. The master code will be enabled only for the modules that are working as a master while the slave code will be enable in all the modules.

Figure 5 shows a block diagram of the main FPGA. All the FPGA logic is enabled when the module is configured as a master. However, when the module is configured as a slave, the master logic is disabled. The FrontBus logic receives commands and information from the FrontBus and either executes the communication between the information requested. The VME control block does the communication between the main FPGA and the VME FPGA. This means that the main FPGA access the VME bus only through the VME FPGA. The DAC control block is responsible for retrieving information from the channels, processing it, and controlling the DAC chips. VME registers will configure the processing. The channels block communicates with the FIFO interface. The FIFO interface reads data out of the 10 channels, and during readout transfers data to VME.

Figure 5: Main FPGA Block Diagram

The channels block implements all the following DSP algorithms:

- Leading Edge Discrimination:

- $y_n = x_n x_{n-k}$  (differentiation)

- $y_n = (x_n + x_{n-2}) + x_{n-1} << 1$  (×4, Gaussian filtering)

- Threshold comparison  $\rightarrow$  Lead Edge Discriminator (LED) time

- Constant Fraction Discrimination: (See also David Radford's new CFD)

- $y_n = x_n x_{n-k}$  (differentiation)

- $y_n = (x_n + x_{n-2}) + x_{n-1} \le 1$  (×2, Gaussian filtering)

- $y_n = x_{n-k} f x_n$  (constant fraction, *f* is an attenuation factor)

- Zero crossing comparison  $\rightarrow$  CFD time

- Trapezoidal filter and energy determination (V.T Jordanov, G.F. Knoll, NIM A345 (1994) 337-345)

- $y_n = y_{n-1} + ((x_n + x_{n-2m-k})) (x_{n-m} + x_{n-m-k}))$

- Maximum tracking  $\rightarrow$  energy

- Pole-Zero correction

- $y_n = x_n + I_n / t$  (where *t* is the pre-amplifier time constant)

- $I_n = I_{n-1} + x_n$

The master logic block will be enabled by the master logic enable signal. This signal will be sent by the VME FPGA and will indicate to the main FPGA if it is a master or slave module, which will be determined by a VME register.

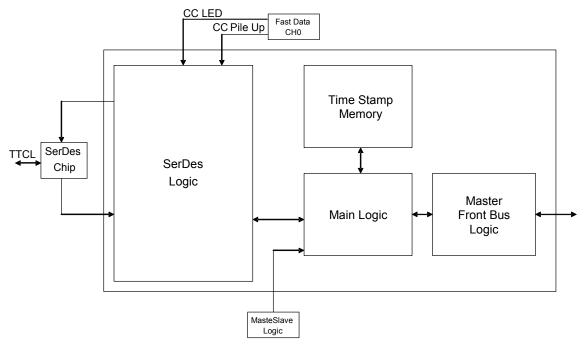

The master logic uses the front panel bus to control the four modules connected to a crystal. Also, it interfaces with the Serializer/Deserializer (SER/DES), which communicates with the Trigger Timing & Control Link (TTCL). Figure 6 shows the block diagram of the FrontBus master logic.

Figure 6: Block Diagram of the FrontBus Master Logic

The Main Logic block controls all the other functional blocks in this algorithm and interprets the TTCL commands. The SER/DES logic is responsible for reading and validating the data package received from the TTCL. This data package is described in reference [3]. Once it validates the data package, it passes it on to the Main Logic block so that the required commands can be executed. The Main Logic block is also responsible for sending the slow and fast hit description data back to the TTCL. This other data package structure is described in reference [1]. The fast hit description data can be the Central Contact Leading Edge Discriminator (CC LED) and/or the Central Contact Pile Up signals that are connected directly to this Main Logic block. The Time Stamp memory (TS Memory) is a set of registers that store all the time stamps that were sent to the TTCL and still point to valid raw data inside the circular buffer.

#### 2.2.4.1 MODES OF OPERATION

UNDER DISCUSSION ... THE CURRENT PROPOSED ETC. The main FPGA will operate in four different modes (see Table 5). We will now describe these modes.

| Mode | Board type               |

|------|--------------------------|

| 00   | Internal                 |

| 01   | External                 |

| 10   | Internal with validation |

| 11   | TTCL                     |

#### Table 5 – Modes of Operation

#### 2.2.4.1.1 INTERNAL MODE

This mode can be used with one single board or one full crate without the TTCL communication. In the internal mode all channels are independent. When the logic detects a leading edge (through the LED algorithm) this will start timers, which will latch the results of the DSP algorithms (energy, CFD, etc) into the header memory. Later, the data from the circular buffer and header is transferred to the pre-buffer memory (for more information on the pre-buffer memory, refer to Section 2.2.4.5). In this mode, all the events will be readout and we don't expect any validation.

#### 2.2.4.1.2 EXTERNAL MODE

This mode can also be used with one single board or one full crate without the TTCL communication. One external trigger signal on the auxiliary inputs is used to start timers, which will latch the results of the DSP algorithms (energy, CFD, etc) into the header memory. This external signal is propagated to all channels so all of them are going to store information even if they didn't have a valid LED. Later, the data from the circular buffer and the header memory, refer to Section 2.2.4.5). In this mode, all the triggered events will be readout and we don't expect any additional validation. The timing specification for this mode is yet to be determined.

## 2.2.4.1.3 INTERNAL WITH VALIDATION MODE

This mode is very similar to the internal mode. However, the data from the circular buffer and header is not automatically transferred to the pre-buffer memory. It waits for an external validation signal, provided through an auxiliary input. The timing specification for this mode is yet to be determined.

#### 2.2.4.1.4 TRIGGER TIMING & CONTROL LINK MODE

While operating in TTCL Mode the digitizers associated with one crystal will be connected to the TTCL through the SER/DES of the master digitizer.

An event will start when the LED associated the crystal central contact (CC) fires. The CC will always be connected to channel 1 of the master digitizer module. The master digitizer informs all crystal channels (through the FB\_LED line) and the TTCL (through the fast data link) that the LED was detected. When the LED signal is detected, the results of the DSP algorithms of all of the enabled channels (energy, CFD, etc) are

latched into the header memory. The master digitizer assigns to this event a specific header memory position. Therefore, all channels will store the DSP algorithm information in the same header memory position. In parallel, the master module will collect information to assemble the trigger buffer. It will calculate the low-resolution energy of the CC and collect the channel hit pattern. When the TTCL demands slow data from the digitizer boards, the master module will then send the information that is in the trigger buffer to the TTCL. The master digitizer will save the time stamp and the header memory position. The modules will then be ready to handle another event or to receive a readout command.

Once the TTCL makes a decision that an event needs to be readout it will send to the digitizer boards a readout command together with the time stamp of the event. The master digitizer module will then compare this time stamp with all the time stamps that it has stored and that are still valid (i.e., for which the raw data are still available inside the circular buffer). If the master digitizer finds a match it will send a readout command to all channels informing them which header memory position needs to be readout. The channels will then transfer the information from the header memory and the raw data to the pre-buffer memory. Later the data is transfer to the external FIFO. If the event is not readout before the circular buffer is overwritten, that particular event is flushed from the header memory.

#### 2.2.4.2 CHECKING SYNCHRONISM

Every channel has its own timer that generates the time stamp. It is therefore necessary to verify that all channels are in sync. Since the sync command will be sent every 2us and we don't want to overload the FrontBus communication, we will divide this task into two parts.

Every time the master digitizer module receives the sync command it will check the TTCL time stamp against the Central Contact time stamp. If they match then no error flag will be set. This will be done every 2us.

At a slower rate, the master digitizer module will check the central contact time stamp against each channel. This will be done by sending a command to latch the current status of all channels as a broadcast command through the FrontBus. Then the master digitizer will broadcast the CC TS and each channel will compare the CC TS with its latched TS. If there is a mismatch the channel will raise an error flag.

The master digitizer will then send a command to get the status of each board. If there is any error it will send an error message to the TTCL. No action besides sending this information to the TTCL will be done. If a TS reset is required, the TTCL will send a specific command asking for that. Otherwise this flag will remain set.

#### 2.2.4.3 INITIALIZATION

#### 2.2.4.3.1 SYSTEM INITIALIZATION

All Digitizers in a crate will behave as slave boards after start up or reset. The VME host sets a register in the Main FPGA that will determine if a board is a Master or Slave Digitizer. After the VME host determines which board is a Master, the Master logic will take control of the crate.

#### 2.2.4.3.2 TRIGGER TIMING & CONTROL LINK INITIALIZATION

During initialization and reset the SER/DES link will be down for some period of time while it locks to the Master Trigger TX signal. After acquiring lock, the system will start receiving clock signals with a 20 ns period. The TTCL will keep the SYNC signal active until its lock signal goes high, meaning that the Master Digitizer Board will start receiving nine words with MSB equal to '0' and LSB equal to '1'.

Once the main FPGA has received a valid clock from the Master Trigger SER/DES and the system reset goes low, the Master Digitizer Board will start sending data to the TTCL. Initially it will send sync data packets that are used to cause the SER/DES chip to acquire lock. After the TTCL SER/DES locks to the Digitizer SER/DES, then it will start sending real data to the Master Digitizer Board.

The SER/DES block of the Master Digitizer Board will transition from Sync Mode to Operating Mode once it receives the first data packet from the Master Trigger board that is different from the sync data. Once the Master Digitizer is out of Sync Mode, different commands will be sent to the Main Logic block of the Master Digitizer (Figure 6) every 5 clocks.

If the lock signal goes down or a reset occurs then the SER/DES Block of the Master Digitizer Board will go back to the sync mode and use the same procedure in order to start receiving commands again.

#### 2.2.4.4 CLOCK MANAGEMENT

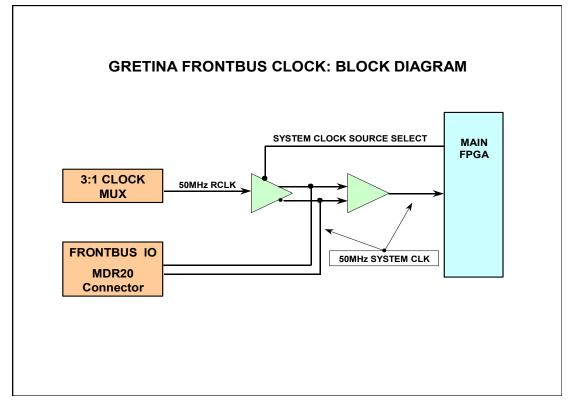

The main FPGA has three clock inputs. One of them comes from the VME FPGA and is always present. The second one is the system clock source that is supplied by the TTCL link, the FrontBus interface, the 50MHz VME reference clock or the external clock Input on the front panel Auxiliary I/O bus. The VME FPGA controls the system clock multiplexer with 2 bits in an internal register that is on the VME Bus.

When a board is operating in stand-alone mode, it may receive the system clock from the internal 50MHz clock distribution or from the Auxiliary I/O external clock input. When 4 boards are operating as an independent crate, the slave boards will receive their clock through the FrontBus and the Main Digitizer Board will receive its clock internal 50MHz clock distribution or from the Auxiliary I/O external clock input.

When working on the TTCL mode the Main Digitizer Board will receive its clock from the recovered clock of the TTCL link and will spread it through the FrontBus to all the slave boards.

#### 2.2.4.5 FIFO AND OUTPUT DATA FORMAT

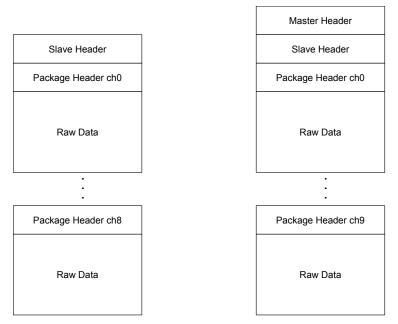

Each ADC channel has a pre-buffer memory. The data are transferred from the prebuffers to the FIFO for VME readout. The structure of the data package can be seen on Figure 7. If the module is a master, additional information, the master header specific to the master functions, is stored in the FIFO for readout.

Figure 7: (a) Data package from a slaver board. (b) Data package from a master board.

The Package header contains the information that belongs to the channels. Its structure is shown in Figure 8.

| 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15            | 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |

|--------------------------------------------------|-------------------------------------------------|

| CH_ID UserDef                                    | Packet length (header included) GA              |

| LED / external timestamp bits 0 - 15*            | LED / external timestamp bits $16 - 31^*$       |

| LED / external timestamp bits 32 - 48*           | Energy bits $0 - 15$                            |

| Energy bit $16 - 24$   x   x   T   S   E   C   P | CFD Timestamp bits $0 - 15$                     |

| CFD Timestamp bits 16 - 31                       | CFD Timestamp bits 32 – 47                      |

| CFD point 1 bits 0 - 15                          | CFD point 1 bits 16 – 31                        |

| CFD point 2 bits 0 - 15                          | CFD point 2 bits $16 - 31$                      |

| Raw data point 0 (Sign extended)                 | Raw data point 1 (Sign extended)                |

| Raw data point 2 (Sign extended)                 | Raw data point 3 (Sign extended)                |

|                                                  |                                                 |

|                                                  |                                                 |

|                                                  | -                                               |

Figure 8: Data Package.

\*The TS is updated at 20ns.

Notes:

GA is geographical address (5 bits)

S is for the sign of the LED crossing. (1 is negative).

E is for external trigger flag (the timestamp is external and LED and CFD are not valid).

C is for CFD valid indicating that a CFD crossing occurred.

P is for pileup flag indicating that the energy is corrupted.

T is for data that was generated by a timeout signal during the TTCL mode.

CH\_ID identify which channel the data package belongs to.

User def are 12 bits for user defined information set by a register accessed by VME.

The slave header contains information from the event that is common to all the channels on that specific board (Figure 9). All Digitizers in a crate produce the Slave Header. The Master Digitizer will add a top-level header to the data packet that is used to identify the start of a new event from a crystal (Figure 10).

| 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 | 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |  |  |

|---------------------------------------|-------------------------------------------------|--|--|

| Board ID Header length                |                                                 |  |  |

| FB_LED bits 0 – 15                    | FB_LED bits16 – 31                              |  |  |

| FB_LED bits 32 – 48                   | HM number                                       |  |  |

| TBD                                   | TBD                                             |  |  |

Figure 9: Slave Header.

| 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 | 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |  |  |

|---------------------------------------|-------------------------------------------------|--|--|

| Board ID                              | Header length                                   |  |  |

| Trigger_TS bits 0 – 15                | Trigger _TS bits 16 – 31                        |  |  |

| Trigger _TS bits 32 – 48              | HM number                                       |  |  |

| Low Resolution Energy TBD             |                                                 |  |  |

Figure 10: Master Header.

## 2.2.4.6 MAIN FPGA REGISTERS

The value xFFFFFFF will be returned when reading registers that are not defined, When reading registers that were not defined they will return the value xFFFFFFFF.

| Description                                                                                               | Address      | Access    | Width |

|-----------------------------------------------------------------------------------------------------------|--------------|-----------|-------|

| Board ID                                                                                                  | 0x00         | R         | 32    |

| Value is the board serial number that is given by the switch conf                                         | iguration    | Bit Value |       |

| value is the board serial humber that is given by the switch cont                                         | iguracion.   | 1         | 0     |

| <pre>Bits[11: 0]: Board Id (Pins 8 down to 4 show Geographical Add:<br/>other pins are set to zero)</pre> | ressing, all | Valu      | ie    |

| Bits[15:12]: TBD                                                                                          |              |           |       |

| Bits[31:16]: FIRMWARE VERSION                                                                             |              |           |       |

| Description                                                      | Address | Access | Width |

|------------------------------------------------------------------|---------|--------|-------|

| Programming Done                                                 | 0x04    | R      | 32    |

| This gives the programming status of the VHDL module as follows. |         | Bit Va | alue  |

| This gives the programming status of the vHDL module as follows. |         | 1      | 0     |

| Bits[9: 0]: Programming status of the channels                   |         |        |       |

| Bit 10: Programming status of the DAC module                     |         |        |       |

| Bit 11: Programming status of the front bus (slave) module       |         |        |       |

| Bit 12: Programming status of the master logic module            |         |        |       |

| Bit 13: Programming status of the Debug module                   |         |        |       |

| Bit 14: Programming status of the FIFO module                    |         |        |       |

| Bit 15: Programming status of the Self Trigger module            |         |        |       |

| Bits[19:16]: TBD                                                 |         |        |       |

| Bit 20: FIFO 0 EF flag                                           |         |        |       |

| Bit 21: FIFO 1 EF flag                                           |         |        |       |

| Bit 22: FIFO 0 PAE flag                                          |         |        |       |

| Bit 23: FIFO 0 HF flag                                           |         |        |       |

| Bit 24: FIFO 0 PAF flag                                          |         |        |       |

| Bit 25: FIFO 0 FF flag                                           |         |        |       |

| Bit 26: FIFO 1 FF flag                                           |         |        |       |

| Bits[31:27]: TBD                                                 |         |        |       |

| Description                                                      | Address      | Access    | Width |

|------------------------------------------------------------------|--------------|-----------|-------|

| External Window                                                  | 0x08         | RW        | 32    |

| External validation window length in clock cycles. Value at rese | et is 0x0190 | Bit Value |       |

| or 4us.                                                          |              | 1         | 0     |

| Bits[10: 0]: External window length                              |              | Valu      | e     |

| Bits[31:11]: TBD                                                 |              |           |       |

| Description                                         | Address | Access    | Width |

|-----------------------------------------------------|---------|-----------|-------|

| Pileup Window                                       | 0x0C    | RW        | 32    |

| Dilem winder length Malus et weet 0x0000 (10xz)     |         | Bit Value |       |

| Pileup window length. Value at reset 0x0400 (10us). |         | 1         | 0     |

| Bits[10: 0]: Pileup window length                   |         | Value     |       |

| Bits[31:11]: TBD                                    |         |           |       |

| Description                                         | Address | Access    | Width |

|-----------------------------------------------------|---------|-----------|-------|

| Noise Window                                        | 0x10    | RW        | 32    |

| Noise winder length Walks at react 0x0040 (640ng)   |         | Bit Value |       |

| Noise window length. Value at reset 0x0040 (640ns). |         | 1         | 0     |

| Bits[ 6: 0]: Noise window length                    |         | Valu      | e     |

| Bits[31:11]: TBD                                    |         |           |       |

| Description                                                     | Address      | Access | Width |

|-----------------------------------------------------------------|--------------|--------|-------|

| External trigger sliding length                                 | 0x14         | RW     | 32    |

| Length before we read the energy when we operate in external tr | igger. Value | Bit Va | lue   |

| at reset 0x0190 (4.0us)                                         |              | 1      | 0     |

| Bits[10: 0]: External trigger sliding length                    |              | Value  | e     |

| Bits[31:11]: TBD                                                |              |        |       |

| Description                                                         | Address    | Access    | Width |

|---------------------------------------------------------------------|------------|-----------|-------|

| Collection time                                                     | 0x18       | RW        | 32    |

| Collection time maximum length (length of the flat top in the       | trapezoid, | Bit Value |       |

| typically set to 0x0020 or 320ns).<br>Value at reset 0x01C2 (4.5us) |            | 1         | 0     |

| Bits[8: 0]: Collection time                                         |            | Valu      | e     |

| Bits[31:9]: TBD                                                     |            |           |       |

| Description                                                    | Address | Access    | Width |

|----------------------------------------------------------------|---------|-----------|-------|

| Integration time                                               | 0x1C    | RW        | 32    |

| Integration time length (length of one side of the trapezoid). |         | Bit Value |       |

| Value at reset 0x01C2 (4.5us)                                  |         | 1         | 0     |

| Bits[8: 0]: Integration time                                   |         | Value     |       |

| Bits[31:9]: TBD                                                |         |           |       |

| Description                        | Address | Access | Width |

|------------------------------------|---------|--------|-------|

| Hardaware status                   | 0x20    | RW     | 32    |

|                                    |         | Bit Va | lue   |

|                                    |         | 1      | 0     |

| Bits[0]: DCM Front Bus Lock signal |         | Locked |       |

| Bits[1]: DCM VME CLK Lock signal   |         | Locked |       |

| Bits[2]: SD Lock signal            |         | Locked |       |

| Bits[15: 3]: TBD                   |         | Valu   | e     |

| Bits[31:16]: TBD                   |         |        |       |

| Description                                                   | Address | Access    | Width |

|---------------------------------------------------------------|---------|-----------|-------|

| Data package user defined data                                | 0x24    | RW        | 32    |

| The data written here will show up at the data package header |         | Bit Value |       |

|                                                               |         | 1         | 0     |

| Bits[11: 0]: User defined data                                |         | Valu      | e     |

| Bits[31:12]: TBD                                              |         |           |       |

| Description                                                      | Address      | Access | Width |

|------------------------------------------------------------------|--------------|--------|-------|

| Control/Status channel #Number                                   | *            | RW     | 32    |

| This register address is the only one that is read/write.        |              | Bit Va | alue  |

| This register address is the only one that is read/write.        |              | 1      | 0     |

| Bit 0: START/STOP. This bit must be set to one for the channel   | to operate.  |        |       |

| Value at reset is 0. Read/Write.                                 |              |        |       |

| Bit 1: Debug Mode. This bit when set to 1 puts the channel in    | n debug mode |        |       |

| operation using internal data. Value at reset 0. (Read/Write)    |              |        |       |

| Bit 2: Pile-up drop-out enable. When this bit is set to one,     |              |        |       |

| drops any event that occurs in a pileup window else it just not. | ifies pileup |        |       |

| through a flag in                                                |              |        |       |

| the event header. Value at reset 1. Read/Write.                  |              |        |       |

| Bits [4:3]: Trigger mode. We have the following configuration:   |              |        |       |

| 00: Internal mode                                                |              |        |       |

| 01: External mode                                                |              |        |       |

| 10: Internal with Validation mode                                |              |        |       |

| 11: TTCS Decision mode                                           |              |        |       |

| Value a reset: 00. Read/Write.                                   |              |        |       |

| Bit 5: CFD Tap delay setup. If set to 0, the tap delay is fi     | lling-up and |        |       |

| no event can be acquired. Read-only.                             |              |        |       |

| Bit 6: Tap delay 1 setup. If set to 0, the tap delay is filling  | ng-up and no |        |       |

| event can be acquired. Read-only.                                |              |        |       |

| Bit 7: Tap delay 2 setup. If set to 0, the tap delay is filling  | ng-up and no |        |       |

| event can be acquired. Read-only.                                |              |        |       |

| Bit 8: Tap delay 3 setup. If set to 0, the tap delay is filling  | ng-up and no |        |       |

| event can be acquired. Read-only.                                |              |        |       |

| Bit 9: Tap delay 4 setup. If set to 0, the tap delay is filling  | ng-up and no |        |       |

| event can be acquired. Read-only.                                |              |        |       |

| Bits [11:10]: Polarity validation. Value at reset 11.            |              |        |       |

| 01: only positive trigger considered                             |              |        |       |

| 10: only negative trigger considered                             |              |        |       |

| 11: both triggers considered                                     |              |        |       |

| 00: no trigger considered (the LED still fires                   |              |        |       |

| externally though, as opposed to                                 |              |        |       |

| START/STOP) Read/Write.                                          |              |        |       |

| Bit 12: Select CFD. (not implemented)                            |              |        |       |

| Bit 13: Select Pole-zero (not implemented)                       |              |        |       |

| Bit 14: TBD                                                      |              |        |       |

| Bit 15: Pre-buffer Ready flag                                    |              |        |       |

| Bits[31:16]: TBD                                                 |              |        |       |

• There is one of this registers for each channels and their address are specified by the next table

| Description              | Address | Access | Width |

|--------------------------|---------|--------|-------|

| Control/Status channel 0 | 0x40    | RW     | 32    |

| Control/Status channel 1 | 0x44    | RW     | 32    |

| Control/Status channel 2 | 0x48    | RW     | 32    |

| Control/Status channel 3 | 0x4C    | RW     | 32    |

| Control/Status channel 4 | 0x50    | RW     | 32    |

| Control/Status channel 5 | 0x54    | RW     | 32    |

| Control/Status channel 6 | 0x58    | RW     | 32    |

| Control/Status channel 7 | 0x5C    | RW     | 32    |

| Control/Status channel 8 | 0x60    | RW     | 32    |

| Control/Status channel 9 | 0x68    | RW     | 32    |

| Description                                                                                                                                                                                                                                                                         | Address     | Access | Width |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|-------|

| LED Threshold                                                                                                                                                                                                                                                                       | *           | RW     | 32    |

| This is the Leading Edge Discriminator (LED) threshold. Only bi                                                                                                                                                                                                                     | ts 17 to 0  | Bit Va | lue   |

| are used. This is an unsigned value and the three lower bits precision bit. (The dot is between bit 3 and 2). The value at reset is $0x1FFFF$ (full range so that no event shoul It is internally converted to a signed value depending on how t the current sample is. Write-only. | d trigger). | 1      | 0     |

| Bits[16: 0]: LED Threshold                                                                                                                                                                                                                                                          |             | Valu   | e     |

| Bits[31:18]: TBD                                                                                                                                                                                                                                                                    |             |        |       |

\* There is one of this registers for each channels and their address are specified by the next table.

| Description     | Address | Access | Width |

|-----------------|---------|--------|-------|

| LED Threshold 0 | 0x80    | RW     | 32    |

| LED Threshold 1 | 0x84    | RW     | 32    |

| LED Threshold 2 | 0x88    | RW     | 32    |

| LED Threshold 3 | 0x8C    | RW     | 32    |

| LED Threshold 4 | 0x90    | RW     | 32    |

| LED Threshold 5 | 0x94    | RW     | 32    |

| LED Threshold 6 | 0x98    | RW     | 32    |

| LED Threshold 7 | 0x9C    | RW     | 32    |

| LED Threshold 8 | 0XA0    | RW     | 32    |

| LED Threshold 9 | 0xA4    | RW     | 32    |

| Description                                                                                                                                                                                                                                                                                                                                       | Address             | Access | Width |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|-------|

| CFD Parameters                                                                                                                                                                                                                                                                                                                                    | *                   | RW     | 32    |