# **GRETA VHDL MODULES**

# I - TapDelay

This module implements a programmable length free running Tap Delay. The maximum speed at which it can run is 182MHz (internal speed without driving the output outside). The following table summarizes the input/output of this block:

| Signal Name      | Description                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------|--|--|--|--|--|

| RESET            | Asynchronous reset. It is active high                            |  |  |  |  |  |

| CLK              | Clock.                                                           |  |  |  |  |  |

| LOAD             | This synchronous signal indicates when we want to load a new     |  |  |  |  |  |

|                  | delay length. It resets the status line to zero as well as the   |  |  |  |  |  |

|                  | internal counters.                                               |  |  |  |  |  |

| STATUS           | Goes high when the Tap delay is filled up and ready to have      |  |  |  |  |  |

|                  | valid input output relation for filtering. It goes low each time |  |  |  |  |  |

|                  | the LOAD signal is asserted and goes back up when ready for      |  |  |  |  |  |

|                  | operation.                                                       |  |  |  |  |  |

| LENGTH(8 to 0)   | The bus giving the programmable length to be loaded.             |  |  |  |  |  |

| DATAin(15 to 0)  | Input of the Tap delay X <sub>n</sub>                            |  |  |  |  |  |

| DATAout(15 to 0) | Output of the Tap delay Xn-L                                     |  |  |  |  |  |

Table 1: Tap Delay I/Os

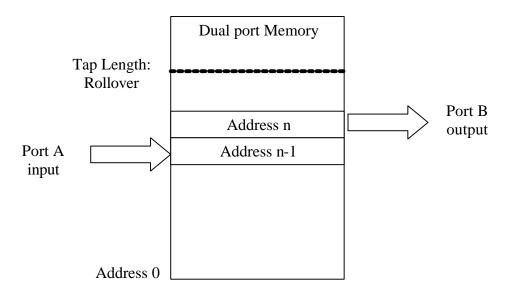

The basic architecture is as follows:

The resources used are as follows: Slices: 21 Block RAM: 1

## II – DiffFilt

This module implements the differentiation filter. It simply does a 2's complement, which is no less than a modified adder (with the first carry set to 1). We must note that performing  $X_n-X_{n-k}$  correspond to doing  $X_n + (not X_{n-k}) + 1$ . We must however note that the addition is one bit wider since we have to extend the sign to accommodate for the 2's complement sign extension. The speed is around 380MHz.

| Signal Name                                                   | Description                                           |  |  |  |

|---------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| RESET Asynchronous reset. It is active high                   |                                                       |  |  |  |

| CLK                                                           | Clock.                                                |  |  |  |

| Xn(11 to 0)                                                   | The sample Xn in 2's complement representation        |  |  |  |

| Xn_k(11 to 0)The sample Xn-k in 2's complement representation |                                                       |  |  |  |

| Yn(12 to 0)                                                   | Output of the filter in 2's complement representation |  |  |  |

|                                                               | Table 2: Differentiation filter I/Os                  |  |  |  |

The resources used are as follows: Slices: 13 Block RAM: 0

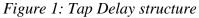

## III – GauFilt1

This module implements a first stage (13 bit input) three point Gaussian filter. It implements the following equation:

$(X_n + X_{n-2}) + X_{n-1} << 1$

The speed is around 220MHz.

The following graph describe the internal architecture:

Figure 2: Gaussian Filter first stage architecture

We must note that we loose 1 pipeline delay by doing the addition between  $(X_n + X_{n-2})$  but that it saves resources in terms of adder length and intermediary storage register. We do not really care about the delay in the result since it is only one clock cycle delay and we have to take the entire pipeline into account anyways. In addition, if we are required to pipeline the ripple carry adder (look-ahead adder does not seem appropriate due to the extra space required for the small speed gained). In addition since we are operating in 2's complement representation, we cannot use the Carry out as the MSB but we need to extend the operands for a proper MSB. This is due to the fact that in 2's complement the carry out must be combined to the eventual signed bit to have a meaning.

| Signal Name         Description |                                                       |  |  |  |

|---------------------------------|-------------------------------------------------------|--|--|--|

| RESET                           | Asynchronous reset. It is active high                 |  |  |  |

| CLK                             | Clock.                                                |  |  |  |

| Xn(12 to 0)                     | The sample Xn in 2's complement representation        |  |  |  |

| Yn(14 to 0)                     | Output of the filter in 2's complement representation |  |  |  |

|                                 | Table 3: Gaussian filter stage 1 1/0s                 |  |  |  |

Table 3: Gaussian filter stage 1 I/Os

The resources used are as follows: Slices: 40 Block RAM: 0

### IV – GauFilt2

This module implements a second stage (15 bit input) three point Gaussian filter. It implements the following equation:

$(X_n + X_{n-2}) + X_{n-1} << 1$

The speed is around 197MHz (slower than the previous stage). The architecture is the same as the one used for *GauFilt1*.

| Signal Name | Description                                           |  |  |  |

|-------------|-------------------------------------------------------|--|--|--|

| RESET       | Asynchronous reset. It is active high                 |  |  |  |

| CLK         | Clock.                                                |  |  |  |

| Xn(14 to 0) | The sample Xn in 2's complement representation        |  |  |  |

| Yn(16 to 0) | Output of the filter in 2's complement representation |  |  |  |

Table 4: Gaussian filter stage 2 I/Os

The resources used are as follows: Slices: 48 Block RAM: 0

## V – LED

V2.5

This module combine all the blocks needed to generate the Leading Edge Discriminator timing. It is composed of some sub-modules that are not reused anywhere else.

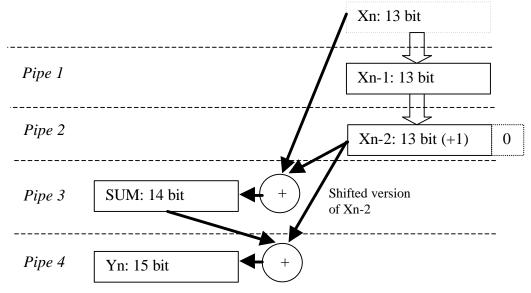

### V.1 – VTHCross

This sub-module computes the crossing of a rising edge above a threshold or the crossing of a falling edge under a negative threshold. It is using only the carry of a subtraction and therefore only the carry generation is implemented. For speed reason since we also need to generate a signed version of the threshold a direct implementation using Virtex blocks has been used. The following flow chart shows the implementation:

| Signal Name                      | Description                                                         |  |  |  |

|----------------------------------|---------------------------------------------------------------------|--|--|--|

| RESET                            | Asynchronous reset. It is active high                               |  |  |  |

| CLK                              | Clock.                                                              |  |  |  |

| LOADVTH                          | A synchronous pulse used to load the threshold value                |  |  |  |

| VTH(14 to 0)                     | The unsigned representation of the threshold                        |  |  |  |

| INPUT(15 to 0)                   | JT(15 to 0) Input sample                                            |  |  |  |

| SIGN                             | Indicate if the crossing is positive or negative                    |  |  |  |

| CROSSING                         | The result. Set to one if threshold crossed above VTH or below -VTH |  |  |  |

| Table 5: Threshold crossing I/Os |                                                                     |  |  |  |

Figure 3: Threshold crossing structure

### V.2 – NoiseTimer

This sub-module implements the Noise Timer used as a programmable dead-time. It uses a simple counter that starts counting on a START signal and stops when the programmable length is reached.

| Signal Name      | Description                                                          |  |  |  |

|------------------|----------------------------------------------------------------------|--|--|--|

| RESET            | Asynchronous reset. It is active high                                |  |  |  |

| CLK              | Clock.                                                               |  |  |  |

| START            | The synchronous start pulse (should be valid only one clock cycle)   |  |  |  |

| CLEAR            | A synchronous line disabling the counter and bringing any current    |  |  |  |

|                  | noise window to ready.                                               |  |  |  |

| LOADNoise        | The synchronous load pulse for storing the window length             |  |  |  |

| WinNoise(6 to 0) | Noise window length                                                  |  |  |  |

| DISABLED         | The disable line indicating that the system is still under the noise |  |  |  |

|                  | window condition.                                                    |  |  |  |

Table 6: Noise Timer I/Os

### V.3 –VTHProcess

This sub-module implements the final processing required for the Leading edge Discriminator by combining the different windows with the crossing line to generate the timestamp pulse.

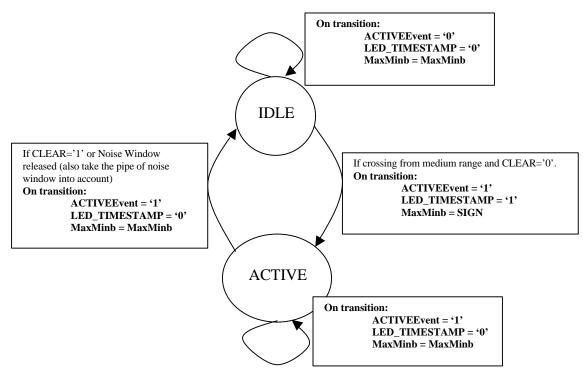

It is implemented as a state machine with two states as described below.

Figure 4: VTHProcess Structure

| Signal Name   | Description                                                              |  |  |  |  |

|---------------|--------------------------------------------------------------------------|--|--|--|--|

| RESET         | Asynchronous reset. It is active high                                    |  |  |  |  |

| CLK           | Clock.                                                                   |  |  |  |  |

| CLEAR         | A synchronous line forcing the state into idle                           |  |  |  |  |

| DISABLED      | The synchronous signal coming from the Noise Timer module                |  |  |  |  |

| CROSSING      | A synchronous signal coming from VTHCrossing indicating a trigger        |  |  |  |  |

|               | condition has been detected                                              |  |  |  |  |

| SIGN          | Input signal indicating the sign of the crossing                         |  |  |  |  |

| MaxMinb       | A synchronous signal indicating the sign of the previous crossing.       |  |  |  |  |

| ACTIVEEvent   | Output signal indicating an event is being processed                     |  |  |  |  |

| LED_TIMESTAMP | A synchronous pulse indicating when the timestamp should be recorded. It |  |  |  |  |

|               | is also used for starting the Noise Timer                                |  |  |  |  |

|               | Table 7. VTHProcess I/Os                                                 |  |  |  |  |

Table 7: VTHProcess I/Os

#### V.4 –LED

This is the main module. It integrates all the previous modules and various filter modules. The speed is around 214MHz.

| Signal Name   | Description                                                                |  |  |  |  |

|---------------|----------------------------------------------------------------------------|--|--|--|--|

| RESET         | Asynchronous reset. It is active high                                      |  |  |  |  |

| CLK           | Clock.                                                                     |  |  |  |  |

| CLEAR         | A synchronous line forcing the state into idle and RESETEvent high         |  |  |  |  |

| Xn (110)      | The current sample Xn in 2's complement representation                     |  |  |  |  |

| Xn_k (110)    | The sample delayed by k clock cycles in 2's complement representation      |  |  |  |  |

| LOADVTH       | A synchronous pulse indicting that the VTH input has to be latch into the  |  |  |  |  |

|               | internal threshold register.                                               |  |  |  |  |

| VTH (140)     | The unsigned value of the threshold. It is one bit less since the MSB is 0 |  |  |  |  |

|               | when converted to 2's complement.                                          |  |  |  |  |

| LOADNoise     | A synchronous pulse indicting that the noise window length has to be latch |  |  |  |  |

|               | into the internal register.                                                |  |  |  |  |

| WinNoise (60) | The noise window length in unsigned representation                         |  |  |  |  |

| ACTIVEEvent   | Output status line indicating that an event is being processed.            |  |  |  |  |

| MaxMinb       | A synchronous signal indicating the sign of the previous crossing.         |  |  |  |  |

| LED_TIMESTAMP | A synchronous pulse indicating when the timestamp should be recorded. It   |  |  |  |  |

|               | is also used for starting the Noise Timer                                  |  |  |  |  |

|               | Table 8: IED 1/0s                                                          |  |  |  |  |

Table 8: LED I/Os

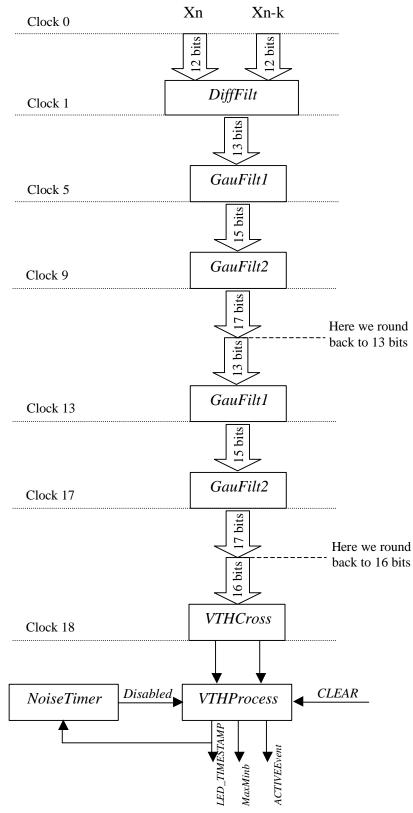

The following flow chart describes the full LED algorithm implementation using the previous blocks. For indication the bus sizes have been added.

Figure 6: Leading Edge Discriminator (LED) Flow Chart

The resources used are as follows: Slices: 120 Block RAM: 0

## VI – CFD

V2.5

This module combines all the blocks needed to generate the Constant Fraction Discriminator timing. It is composed of some sub-modules that are not reused anywhere else. It is composed of some sub-modules that are not reused anywhere else.

#### VI.1 – MULTMinusa

This sub-module implements a multiplication by -1, -2, -4 and -8. It is basically a four-toone multiplexer depending on the 'a' value coded with 2 bits. The following table gives the relation between the 'a' value and the multiplication performed.

| <i>'a'</i> Value | Multiplication |  |  |

|------------------|----------------|--|--|

| 00               | -1             |  |  |

| 01               | -2             |  |  |

| 10               | -4             |  |  |

| 11               | -8             |  |  |

Table 9: Multiplication equivalence

We must note that it adds 1 to the result so that we actually have: OUTPUT = -a.INPUT + 1.

It is using the dedicated internal multiplexer 4-to-1 between two LUT in a slice. It runs around 366MHz.

| Signal Name    | Description                                          |  |  |  |

|----------------|------------------------------------------------------|--|--|--|

| RESET          | Asynchronous reset. It is active high                |  |  |  |

| CLK            | Clock.                                               |  |  |  |

| LOADa          | The synchronous load pulse for storing the 'a' value |  |  |  |

| a(10)          | The value of 'a' as described in table 9             |  |  |  |

| INPUT(15 to 0) | The input value in 2's complement representation     |  |  |  |

| OUTPUT(180)    | The output value in 2's complement representation.   |  |  |  |

|                | $T_{-1}$                                             |  |  |  |

Table 10: MULTMinusa I/Os

The resources used are as follows: Slices: 17 Block RAM: 0

8

### VI.2 – Magnitude

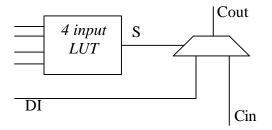

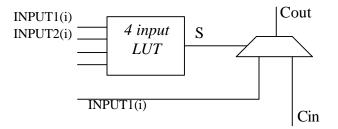

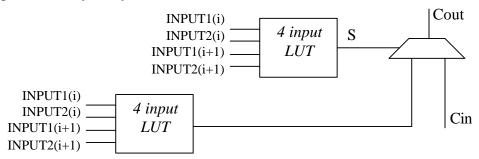

This sub-module implements a magnitude discriminator (similar to a leading edge crossing algorithm). However, the threshold used here does not span the full range since we only need small thresholds. It also allows reducing the logic needed since the carry can be propagated twice as fast for the upper bits. Since the LUT inside the Xilinx have four inputs, it is possible to compute two carry at once when the threshold is sign extended.

| Signal Name    | Description                                                    |  |  |  |

|----------------|----------------------------------------------------------------|--|--|--|

| RESET          | Asynchronous reset. It is active high                          |  |  |  |

| CLK            | Clock.                                                         |  |  |  |

| LOADThreshold  | The synchronous load pulse for storing the threshold value     |  |  |  |

| Threshold(40)  | The threshold value in unsigned representation                 |  |  |  |

| INPUT(11 to 0) | The input value in 2's complement representation               |  |  |  |

| ENABLE         | A synchronous pulse indicating that the magnitude of the input |  |  |  |

|                | signal is above the threshold.                                 |  |  |  |

Table 11: Magnitude I/Os

The following table and figure tries to summarize the two carries generation at once through the fast carry chain.

Figure 7: Fast Carry logic VirtexII Xilinx block

| Cin | INPUT(i) | not  | Local | INPUT(i+1) | Cout | Comment                              |

|-----|----------|------|-------|------------|------|--------------------------------------|

|     |          | SIGN | carry |            |      |                                      |

| 0   | 0        | 0    | 0     | 0          | 0    |                                      |

| 1   | 0        | 0    | 0     | 0          | 0    |                                      |

| 0   | 1        | 0    | 0     | 0          | 0    |                                      |

| 1   | 1        | 0    | 1     | 0          | 0    |                                      |

| 0   | 0        | 1    | 0     | 0          | 0    | Spot taken by the Cin decode MUX     |

| 1   | 0        | 1    | 1     | 0          | 1    | Needed to decode Cin                 |

| 0   | 1        | 1    | 1     | 0          | 1    | Only represented by SIGN outside the |

| 1   | 1        | 1    | 1     | 0          | 1    | Cin Decode MUX                       |

| 0   | 0        | 0    | 0     | 1          | 0    |                                      |

| 1   | 0        | 0    | 0     | 1          | 0    |                                      |

| 0   | 1        | 0    | 0     | 1          | 0    | Spot taken by the Cin decode MUX     |

| 1   | 1        | 0    | 1     | 1          | 1    | Needed to decode Cin                 |

| 0   | 0        | 1    | 0     | 1          | 1    |                                      |

| 1   | 0        | 1    | 1     | 1          | 1    | Only represented by "not SIGN"       |

| 0   | 1        | 1    | 1     | 1          | 1    | outside the Cin Decode MUX           |

| 1   | 1        | 1    | 1     | 1          | 1    |                                      |

Table 12: Two carry fast propagation logic

We can therefore have the following equations:

- DI is "not INPUT(11)" for representing "not SIGN"

- S is "((not INPUT(11)) and (not INPUT(i)) and (not INPUT(i+1))) or (INPUT(11) and INPUT(i) and INPUT(i+1))" for decoding Cin

The resources used are as follows: Slices: 8

Block RAM: 0

### VI.3 – TapDelayLoc

This sub-module implements a programmable length free running Tap Delay using local distributed memory. The maximum length for this delay is 64 taps. It is using the same architecture described in figure 1.

| Description                                                      |  |  |

|------------------------------------------------------------------|--|--|

| Asynchronous reset. It is active high                            |  |  |

| Clock.                                                           |  |  |

| This synchronous signal indicates when we want to load a new     |  |  |

| delay length. It resets the status line to zero as well as the   |  |  |

| internal counters.                                               |  |  |

| Goes high when the Tap delay is filled up and ready to have      |  |  |

| valid input output relation for filtering. It goes low each time |  |  |

| the LOAD signal is asserted and goes back up when ready for      |  |  |

| operation.                                                       |  |  |

| The bus giving the programmable length to be loaded.             |  |  |

| Input of the Tap delay X <sub>n</sub>                            |  |  |

| Output of the Tap delay Xn-L                                     |  |  |

|                                                                  |  |  |

Table 13: Tap Delay Local I/Os

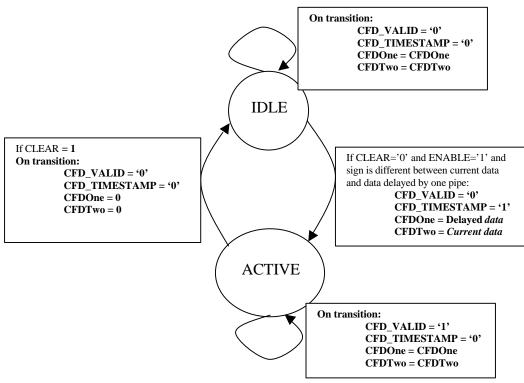

#### VI.4 – CFDProcess

This sub-module implements the CFD processing. It detects a zero crossing (both directions are detected to accommodate both polarities). It is implemented as a state machine with two states as described below.

We must note that the data is truncated from 20bits to 16 bits at this level.

Figure 8: CFDProcess Structure

| Signal Name      | Description                                                        |  |  |

|------------------|--------------------------------------------------------------------|--|--|

| RESET            | Asynchronous reset. It is active high                              |  |  |

| CLK              | Clock.                                                             |  |  |

| CLEAR            | A synchronous pulse indicating that the event has been             |  |  |

|                  | processed or that the system is disabled and that we can reset all |  |  |

|                  | the values corresponding to it                                     |  |  |

| ENABLE           | A synchronous pulse indicating that the signal magnitude is        |  |  |

|                  | above a given threshold.                                           |  |  |

| CFDData(19 to 0) | The input value in 2's complement representation.                  |  |  |

| CFDOne(15 to 0)  | First point of the CFD in 2's complement.                          |  |  |

| CFDTwo(15 to 0)  | Second point of the CFD in 2's complement.                         |  |  |

| CFD_VALID        | A line indicating that the CFD points are valid for the current    |  |  |

|                  | event                                                              |  |  |

| CFD_TIMESTAMP    | A synchronous pulse indicating when the timestamp should be        |  |  |

|                  | recorded.                                                          |  |  |

Table 14: CFD Process I/Os

#### VI.5 –CFD

This is the main module. It integrates all the previous modules and various filter modules. The speed is around 161MHz (the speed estimation is flawed here because the routing includes the distributed RAM and it will change when the code is compiled for the final design/The speed can be improved if we pipe the RAM output data).

| Signal Name       | Description                                                      |  |  |  |

|-------------------|------------------------------------------------------------------|--|--|--|

| RESET             | Asynchronous reset. It is active high                            |  |  |  |

| CLK               | Clock.                                                           |  |  |  |

| CLEAR             | A synchronous pulse indicating that the event has been           |  |  |  |

|                   | processed and that we can reset all the values corresponding to  |  |  |  |

|                   | it                                                               |  |  |  |

| LOADThreshold     | The synchronous load pulse for storing the threshold value       |  |  |  |

| Threshold(40)     | The threshold value in unsigned representation                   |  |  |  |

| LOADa             | The synchronous load pulse for storing the 'a' value             |  |  |  |

| a(10)             | The value of 'a' as described in table 9                         |  |  |  |

| LOADTAPLength     | This synchronous signal indicates when we want to load a new     |  |  |  |

|                   | delay length. It resets the status line to zero as well as the   |  |  |  |

|                   | internal counters.                                               |  |  |  |

| TAPLength(5 to 0) | The bus giving the programmable length to be loaded.             |  |  |  |

| Xn(11 to 0)       | The sample Xn in 2's complement representation                   |  |  |  |

| Xn_k(11 to 0)     | The sample Xn-k in 2's complement representation                 |  |  |  |

| CFDOne(15 to 0)   | First point of the CFD in 2's complement.                        |  |  |  |

| CFDTwo(15 to 0)   | Second point of the CFD in 2's complement.                       |  |  |  |

| TAP_STATUS        | Goes high when the Tap delay is filled up and ready to have      |  |  |  |

|                   | valid input output relation for filtering. It goes low each time |  |  |  |

|                   | the LOAD signal is asserted and goes back up when ready for      |  |  |  |

|                   | operation.                                                       |  |  |  |

| CFD_VALID         | A line indicating that the CFD points are valid for the current  |  |  |  |

|                   | event                                                            |  |  |  |

| CFD_TIMESTAMP     | A synchronous pulse indicating when the timestamp should be      |  |  |  |

|                   | recorded.                                                        |  |  |  |

Table 15: CFD I/Os

The resources used are as follows:

Slices: 228 (distributed RAM included) Block RAM: 0

The graph given in figure 9 shows the CFD algorithm implementation using the previous blocks.

Figure 9: CFD algorithm

13

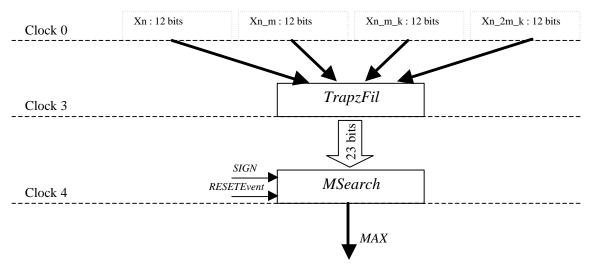

# VII – TrapzFil

V2.5

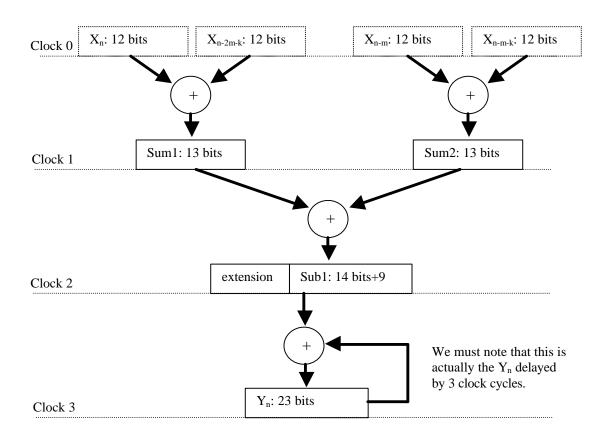

This module implements the computational part of a trapezoidal filter (the tap delay are external to this module). It simply implements the following equation:

$Y_n = Y_{n\text{-}1} + ( \ (X_n + X_{n\text{-}2m\text{-}k}) - (X_{n\text{-}m} + X_{n\text{-}m\text{-}k}) \ )$

It runs around 199MHz.

The following graph describes the internal architecture:

Figure 10: Trapezoidal filter architecture

| Signal Name      | Description                                              |  |  |  |  |

|------------------|----------------------------------------------------------|--|--|--|--|

| RESET            | Asynchronous reset. It is active high                    |  |  |  |  |

| CLK              | Clock.                                                   |  |  |  |  |

| Xn(11 to 0)      | The sample $X_n$ in 2's complement representation        |  |  |  |  |

| Xn_m(11 to 0)    | The sample $X_{n-m}$ in 2's complement representation    |  |  |  |  |

| Xn_m_k(11 to 0)  | The sample $X_{n-m-k}$ in 2's complement representation  |  |  |  |  |

| Xn_2m_k(11 to 0) | The sample $X_{n-2m-k}$ in 2's complement representation |  |  |  |  |

| Yn(22 to 0)      | The result $Y_n$ in 2's complement representation        |  |  |  |  |

|                  | Table 16: TrapzFil I/Os                                  |  |  |  |  |

The resources used are as follows: Slices: 54 Block RAM: 0

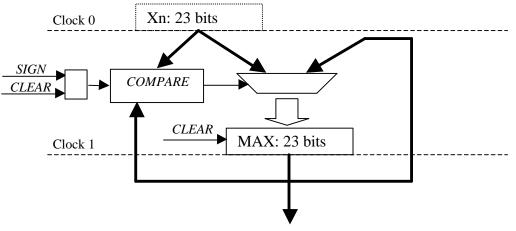

### VIII – MSearch

V2.5

This module implements the extremum search given a minimum/maximum flag. It uses several sub-modules described in the following sections.

#### VIII.1 – COMPARE

This submodule finds the sign of the difference between the two inputs and generates an update signal if the sign line validates the result.

As the sign computation is performed over 23 bits and must be used to multiplex two values, we must be as quick as possible to compute it.

Version 1: generate the update signal using 12 slices.

This version uses the simplest carry chain with a cascade of 23 MUXCY:

Figure 11: simple COMPARE architecture

Version 2: generate the update signal using 18 slices.

This version uses two LUTs and uses only half the carry chain length since we compute the carry every other one.

Figure 12: parallel COMPARE architecture

| Signal Name     | Description                                                     |

|-----------------|-----------------------------------------------------------------|

| INPUT1(22 to 0) | The new sample in 2's complement                                |

| INPUT2(22 to 0) | The sample to compare to in 2's complement                      |

| SIGN            | A synchronous signal indicating a min or max search             |

| UPDATE          | A synchronous pulse indicating that the compare value has to be |

|                 | updated with the new sample.                                    |

Table 17: COMPARE I/Os

#### VIII.2 – MSearch

This module integrates the extremum detection and storage.

With version 2: 153MHz operation With version 1: 179MHz operation

It seems that even though version 2 looks more promising on paper, the LUT to MUXCY routing takes longer than 11 MUXCY to MUXCy propagation. Since it goes fast enough the simplementation was implemented:

Figure 13: MSearch Structure

| Signal Name  | Description                                                          |

|--------------|----------------------------------------------------------------------|

| RESET        | Asynchronous reset. It is active high                                |

| CLK          | Clock.                                                               |

| Xn(22 to 0)  | The sample to compare to the current extremum in 2's complement      |

| CLEAR        | A synchronous pulse indicating that the event has been processed     |

|              | and that we can reset all the values corresponding to it. It also    |

|              | indicates that a new sign has to be updated for the next tracking.   |

| SIGN         | A synchronous signal indicating a min or max search at the time of a |

|              | CLEAR (for next extremum tracking).                                  |

| MAX(22 to 0) | The current extremum in 2's complement                               |

|              | Table 18: MSearch 1/Os                                               |

Table 18: MSearch I/Os

The resources used are as follows: Slices: 24 Block RAM: 0

## IX – ENERGY

This module integrates the trapezoidal filter with the extremum search in order to create the energy value. It runs at about 180MHz (The routing to the COMPARE block is a little bit more efficient when used in the middle of a design).

The following figure summarizes the overall pipeline for the energy computation:

Figure 14: Energy computation structure

| Signal Name           | Description                                                      |  |  |

|-----------------------|------------------------------------------------------------------|--|--|

| RESET                 | Asynchronous reset. It is active high                            |  |  |

| CLK                   | Clock.                                                           |  |  |

| Xn(11 to 0)           | The sample X <sub>n</sub> in 2's complement representation       |  |  |

| Xn_m(11 to 0)         | The sample X <sub>n-m</sub> in 2's complement representation     |  |  |

| Xn_m_k(11 to 0)       | The sample $X_{n-m-k}$ in 2's complement representation          |  |  |

| Xn_2m_k(11 to 0)      | The sample $X_{n-2m-k}$ in 2's complement representation         |  |  |

| CLEAR                 | A synchronous pulse indicating that the event has been processed |  |  |

|                       | and that we can reset all the values corresponding to it.        |  |  |

| SIGN                  | A synchronous signal indicating a min or max search (valid when  |  |  |

|                       | CLEAR is active)                                                 |  |  |

| MAX(22 to 0)          | The current extremum in 2's complement                           |  |  |

| Table 19: Energy I/Os |                                                                  |  |  |

The resources used are as follows: Slices: 79 Block RAM: 0

## X – TIMER

This module is the main timer with 48bit precision (up to 78 hours at 100MHz). It has a main synch signal so that all channels can have the same reference. The circuit operates around 197MHz.

| onous reset. It is active high                              |

|-------------------------------------------------------------|

|                                                             |

|                                                             |

| onous pulse use to reset the timer (used to synchronize all |

|                                                             |

| ent time                                                    |

| )                                                           |

Table 20: TIMER I/Os

The resources used are as follows:

Slices: 48 (the average number will be reduced when combined with other logic). Block RAM: 0

## XI – ProcCORE

This module is the main processing core for one channel. It handles all events and is responsible for creating the packet.

The available status lines from the processing units are:

- TAPDelay1\_STATUS

- o TAPDelay2\_STATUS

- o TAPDelay3\_STATUS

- o TAPDelay4\_STATUS

- TAPDelayLoc1\_STATUS

- o ACTIVEEvent

- CFD\_VALID

It must generate the following control line for the processing units:

- CLEAR

- o LOADTap1

- o LOADTap2

- o LOADTap3

- o LOADTap4

- o LOADTapLoc1

- LOAD LEDTH

- LOAD LEDTimer

- LOAD\_CFDTH

- LOAD\_CFDa

Note: for all the 'LOADxxx' lines, the data must also be presented at the right time.

V2.5

It receives the following data oriented line/busses:

- LED\_TIMESTAMP

- LED\_SIGN

- CFD\_TIMESTAMP

- CFD\_ONE

- CFD\_TWO

- o MAX

It must accommodate the following external parameters:

- PileUp Window (10bits for 10us)

- External Validation Window (11bits for 20us after)

- External Sliding length (11 bits for 20us)

- Raw Data Sliding length (11 bits for 20us)

- Raw Data window length (10 bits for up to 10us)

- LED Threshold (16 bits)

- **CFD Threshold (5 bits)**

- CFD fraction (2 bits)

- BoardID (13 bits: three are generated internally for the 8 channels)

- o Trigger mode (Internal, External, Internal with validation)

- Start/Stop acquisition

- **Debug mode**

- External trigger

- Timer Synch.

- External FIFO busy

The bold items in the previous lists may be different (at the parameter level) for all the channels. This increases the number of VME-based configuration values. The programming register cannot be read back as it would involve too much multiplexing to send it back out through one bus especially since those value are stored close to their processing unit for speed reasons.

The following configuration register are used for setting up the system:

| Register Name    | Address<br>(Word | Description                                                  |

|------------------|------------------|--------------------------------------------------------------|

|                  | aligned)         |                                                              |

| Board ID         | 0x00             | Value is given by the switch configuration. Only 8 bits will |

|                  |                  | be used.                                                     |

|                  |                  | Read-Only                                                    |

| Programming Done | 0x01             | Bit 7 to 0: Gives the current programming status on all      |

|                  |                  | channels                                                     |

|                  |                  | Bit 8: Gives the programming status on the debug module      |

|                  |                  | Bit 9: Gives the programming status on the DACs              |

|                  |                  | Bit 10: and FIFO 0 EF flag.                                  |

|                  |                  | Bit 11: and FIFO 1 EF flag.                                  |

| Register Name                | Address<br>(Word<br>aligned) | Description                                               |

|------------------------------|------------------------------|-----------------------------------------------------------|

|                              |                              | Bit 12: and FIFO 0 PAE flag.                              |

|                              |                              | Bit 13: and FIFO 0 HF flag.                               |

|                              |                              | Bit 14: and FIFO 0 PAF flag.                              |

|                              |                              | Bit 15: and FIFO 0 FF flag and FIFO 1 FF flag.            |

|                              |                              | Read-Only                                                 |

| External Window              | 0x02                         | External validation window length                         |

|                              |                              | (only bit 10 to 0 are used)                               |

|                              |                              | Value at reset is 0x07FF                                  |

|                              |                              | Write-only                                                |

| Pileup Window                | 0x03                         | Pileup-window length                                      |

| Theap whileow                | UNUS                         | (only bit 10 to 0 are used)                               |

|                              |                              | Value at reset 0x0400 (10us)                              |

|                              |                              | Write-only                                                |

| Noise Window                 | 0x04                         | Noise window length                                       |

| Tronse window                | UXU I                        | (only bit 6 to 0 are used)                                |

|                              |                              | Value at reset 0x0040 (640ns)                             |

|                              |                              | Write-only                                                |

| External trigger sliding     | 0x05                         | Length before we read the energy when we operate in       |

| length                       | 0.005                        | external trigger.                                         |

| length                       |                              | (only bit 10 to 0 are used)                               |

|                              |                              | Value at reset 0x01C2 (4.5us)                             |

|                              |                              | Write-only                                                |

| Collection time              | 0x06                         | Collection time maximum length (length of the flat top in |

| Concetion time               | 0.00                         | the trapezoid).                                           |

|                              |                              | Only bits 8 to 0 are used.                                |

|                              |                              | Value at reset 0x01C2 (4.5us)                             |

|                              |                              | Write-only                                                |

| Integration time             | 0x07                         | Integration time length (length of one side of the        |

| integration time             | 0.07                         | trapezoid).                                               |

|                              |                              | Only bits 8 to 0 are used.                                |

|                              |                              | Value at reset 0x01C2 (4.5us)                             |

|                              |                              | Write-only                                                |

| Control/Status:              |                              | This register address is the only one that is read/write. |

| Control/Status.<br>Channel 0 | 0x08                         | Bit 15: Pre-buffer Ready flag                             |

| Channel 1                    | 0x08<br>0x09                 | Bit 14-12: Unused for now.                                |

| Channel 2                    | 0x07<br>0x0A                 | Bit 11-10: Polarity validation. Value at reset 11.        |

| Channel 3                    | 0x0A<br>0x0B                 | ( <i>Read/Write</i> ).                                    |

| Channel 4                    | 0x0D<br>0x0C                 | 01: only positive trigger considered                      |

| Channel 5                    | 0x0C<br>0x0D                 | 10: only negative trigger considered                      |

| Channel 6                    | 0x0D<br>0x0E                 | 11: both triggers considered                              |

| Channel 7                    | 0x0E<br>0x0F                 | 00: no trigger considered (the LED still fires            |

|                              | UAUL                         |                                                           |

|                              |                              | externally though, as opposed to START/STOP)              |

|                              |                              | START/STUP)                                               |

| Register Name          | Address      | Description                                                                                                         |

|------------------------|--------------|---------------------------------------------------------------------------------------------------------------------|

|                        | (Word        |                                                                                                                     |

|                        | aligned)     |                                                                                                                     |

|                        |              | Bit 9: Tap delay 4 set-up ( <i>Read-only</i> ). If set to 0, the tap                                                |

|                        |              | delay is filling-up and no event can be acquired.                                                                   |

|                        |              | Bit 8: Tap delay 3 set-up ( <i>Read-only</i> ). If set to 0, the tap                                                |

|                        |              | delay is filling-up and no event can be acquired.                                                                   |

|                        |              | Bit 7: Tap delay 2 set-up ( <i>Read-only</i> ). If set to 0, the tap                                                |

|                        |              | delay is filling-up and no event can be acquired.                                                                   |

|                        |              | Bit 6: Tap delay 1 set-up ( <i>Read-only</i> ). If set to 0, the tap                                                |

|                        |              | delay is filling-up and no event can be acquired.                                                                   |

|                        |              | Bit 5: CFD Tap delay setup. ( <i>Read-only</i> ). If set to 0, the tap                                              |

|                        |              | delay is filling-up and no event can be acquired.                                                                   |

|                        |              | Bit 4-3: Trigger mode. We have the following                                                                        |

|                        |              | configuration:                                                                                                      |

|                        |              | 00/11: Internal mode                                                                                                |

|                        |              | 01: External mode                                                                                                   |

|                        |              | 10: Validation                                                                                                      |

|                        |              | Value a reset: 00. ( <i>Read/Write</i> )                                                                            |

|                        |              | Bit 2: Pile-up drop-out enable. When this bit is set to one,                                                        |

|                        |              | the channel drops any event that occurs in a pileup                                                                 |

|                        |              | window else it just notifies pileup through a flag in                                                               |

|                        |              | the event header. Value at reset 1. <i>Read/Write</i> .                                                             |

|                        |              | Bit 1: Debug Mode. This bit when set to 1 puts the channel                                                          |

|                        |              | in debug mode operation using internal data. Value at reset $O_{\mu}(R_{\mu})$                                      |

|                        |              | at reset 0. ( <i>Read/Write</i> )<br>Bit 0: START/STOP. This bit must be set to one for the                         |

|                        |              |                                                                                                                     |

| LED Threshold:         |              | channel to operate. Value at reset is 0. ( <i>Read/write</i> )                                                      |

| Channel 0              | 0x10         | This is the LED threshold. Only bits 15 to 0 are used. This is an unsigned value and the three lower bits are extra |

| Channel 1              |              | is an unsigned value and the three lower bits are extra                                                             |

| Channel 1<br>Channel 2 | 0x11<br>0x12 | precision bit. (The dot is between bit 3 and 2).<br>The value at reset is 0x7FFF (full range so that no event       |

| Channel 3              | 0x12<br>0x13 | should trigger). It is internally converted to a signed value                                                       |

| Channel 4              | 0x13<br>0x14 | depending on how the sign of the current sample is.                                                                 |

| Channel 5              | 0x14<br>0x15 | Write-only.                                                                                                         |

| Channel 6              | 0x13<br>0x16 | wruc-onuy.                                                                                                          |

| Channel 7              | 0x10<br>0x17 |                                                                                                                     |

| CFD parameters:        |              | Bit 12-7: CFD delay. Value at reset is 0x3F giving a delay                                                          |

| Channel 0              | 0x18         | of 630ns. Write-only                                                                                                |

| Channel 1              | 0x10<br>0x19 | Bit 6-5: CFD fraction. It is a value indicating what fraction                                                       |

| Channel 2              | 0x19<br>0x1A | is used (see table 9 for values). Value at reset is                                                                 |

| Channel 3              | 0x1R<br>0x1B | "00" giving a fraction of 0.5. Write-only                                                                           |

| Channel 4              | 0x1C         | Bit 4-0: CFD threshold. It is an unsigned value of the CFD                                                          |

| Channel 5              | 0x1C<br>0x1D | threshold. The dot is after bit 0. Value at reset is                                                                |

| Channel 6              | 0x1E         | 0x10 (160kev). Write-only                                                                                           |

| Channel 7              | 0x1F         |                                                                                                                     |

| Register Name            | Address  | Description                                                  |

|--------------------------|----------|--------------------------------------------------------------|

| _                        | (Word    | -                                                            |

|                          | aligned) |                                                              |

| Raw Data sliding length: |          | Delay before we start retrieving raw data. Only bits 10 to 0 |

| Channel 0                |          | are used. Value at reset is 0x01C2 (4.5us). Write-only       |

| Channel 1                | 0x20     |                                                              |

| Channel 2                | 0x21     |                                                              |

| Channel 3                | 0x22     |                                                              |

| Channel 4                | 0x23     |                                                              |

| Channel 5                | 0x24     |                                                              |

| Channel 6                | 0x25     |                                                              |

| Channel 7                | 0x26     |                                                              |

|                          | 0x27     |                                                              |

| Raw Data window          |          | Length of raw data retrieved. Only bits 9 to 0 are used.     |

| length:                  | 0x28     | Value at reset is 0x32 (500ns). Write-only                   |

| Channel 0                | 0x29     |                                                              |

| Channel 1                | 0x2A     |                                                              |

| Channel 2                | 0x2B     |                                                              |

| Channel 3                | 0x2C     |                                                              |

| Channel 4                | 0x2D     |                                                              |

| Channel 5                | 0x2E     |                                                              |

| Channel 6                | 0x2F     |                                                              |

| Channel 7                |          |                                                              |

| Debug data buffer        | 0x30     | Used by debug module (see section XIII)                      |

| address                  |          |                                                              |

| Debug data buffer data   | 0x31     | Used by debug module (see section XIII)                      |

Table 21: Configuration Registers

We therefore need 6 bit of address for register configuration.

The event data is organized as a packet that contains a header and the raw data. The packet structure is described below in table 22:

| 0 1 2 3 4 5 6 7 8 9 10 11       | 12    | 13 | 14 | 15                               | 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |

|---------------------------------|-------|----|----|----------------------------------|-------------------------------------------------|

| Board ID                        |       |    |    | Packet length (header included)  |                                                 |

| LED/external Timestamp bit 0-15 |       |    |    | LED/external Timestamp bit 16-31 |                                                 |

| LED/external Timestamp bit 32   | to 47 | 7  |    |                                  | Energy bit 0-15                                 |

| Energy bit 16-22 x x x x x      |       |    |    | CFD Timestamp bit 0-15           |                                                 |

| CFD Timestamp bit 16-31         |       |    |    | CFD Timestamp bit 32-47          |                                                 |

| CFD point 1                     |       |    |    |                                  | CFD point 2                                     |

| Raw data point 0                | х     | Х  | Х  | Х                                | Raw data point 1 x x x x                        |

| Raw data point 2                |       |    |    |                                  | Raw data point 3 x x x x                        |

|                                 |       |    |    |                                  |                                                 |

|                                 |       |    |    |                                  |                                                 |

|                                 |       |    |    |                                  |                                                 |

|                                 |       |    |    |                                  |                                                 |

|                                 |       |    |    |                                  |                                                 |

|                                 |       |    |    |                                  |                                                 |

Note: P is for the pileup flag indicating that the energy is corrupted C is for CFD valid indicating that a CFD crossing occurred.

E is for external trigger flag (the timestamp is external time and not LED, CFD is not valid)

S is for the sign of the LED crossing. (1 negative)

x is for 'not used'

This module contains several sub-modules described in the following sub-sections:

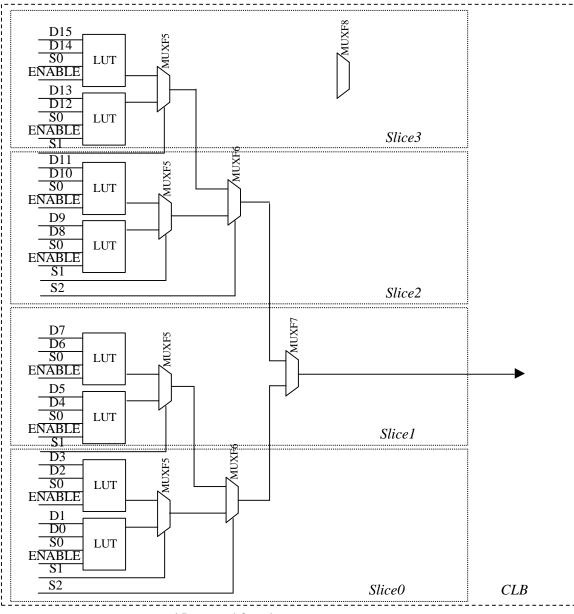

#### XI.1 – MUX16\_16to1

This is a multiplexer 16bits wide, 16 input to 1 output with enable. It is using built-in features of the VirtexII FPGA so that it can operate at full speed (around 141MHz) with the less resource requirement (64 slices). The following diagram shows how the multiplexer is implemented for one bit

| Signal Name      | Description                                          |

|------------------|------------------------------------------------------|

| RESET            | Asynchronous reset. It is active high                |

| CLK              | Clock.                                               |

| ENABLE           | The multiplexer outputs non-zero value when set to 1 |

| S(3 to 0)        | The selection bus                                    |

| INPUT0(15 to 0)  | The input selected by "0000"                         |

| INPUT1(15 to 0)  | The input selected by "0001"                         |

| INPUT2(15 to 0)  | The input selected by "0010"                         |

| INPUT3(15 to 0)  | The input selected by "0011"                         |

| INPUT4(15 to 0)  | The input selected by "0100"                         |

| INPUT5(15 to 0)  | The input selected by "0101"                         |

| INPUT6(15 to 0)  | The input selected by "0110"                         |

| INPUT7(15 to 0)  | The input selected by "0111"                         |

| INPUT8(15 to 0)  | The input selected by "1000"                         |

| INPUT9(15 to 0)  | The input selected by "1001"                         |

| INPUT10(15 to 0) | The input selected by "1010"                         |

| INPUT11(15 to 0) | The input selected by "1011"                         |

| INPUT12(15 to 0) | The input selected by "1100"                         |

| INPUT13(15 to 0) | The input selected by "1101"                         |

| INPUT14(15 to 0) | The input selected by "1110"                         |

| INPUT15(15 to 0) | The input selected by "1111"                         |

| OUTPUT(15 to 0)  | The output                                           |

Table 23: MUX16\_16to1 I/Os

Figure 15: Mux 16 to 1 structure

#### XI.2 – WaitCounter

This module implements three different counters:

- a counter that can start on two different window-lengths. It accommodates the internal delay window and the external delay window. (We then save one counter by using only one). It is possible to combine them, as we use either one or the other. It is gated with a dead time window computed from the sliding and the raw data length.

- a counter with enable used to generate the pre-buffer memory address as well as generate the proper number of raw data point retrieval.

- a counter used to wait until the raw data is ready.

| Signal Name             | Description                                                                 |

|-------------------------|-----------------------------------------------------------------------------|

| RESET                   | Asynchronous reset. It is active high                                       |

| CLK                     | Clock.                                                                      |

| LOADValidationWait      | The external validation length load pulse                                   |

| ValidationWait(10 to 0) | The external validation length                                              |

| LOADExternalWait        | The external trigger sliding length load pulse                              |

| ExternalWait(10 to 0)   | The external trigger sliding length                                         |

| LOADm                   | The integration length load pulse                                           |

| m(8 to 0)               | The integration length                                                      |

| LOADk                   | The collection length load pulse                                            |

| k(8 to 0)               | The collection length                                                       |

| LOADRawLength           | The raw data length load pulse                                              |

| RawLength(9 to 0)       | The raw data length                                                         |

| LOADSlidingWait         | The raw data sliding length load pulse                                      |

| SlidingWait(10 to 0)    | The raw data sliding length                                                 |

| STARTExternalWait       | The synchronous start pulse for external waiting window                     |

| STARTInternalWait       | The synchronous start pulse for internal waiting window                     |

| STARTSlidingWait        | The synchronous start pulse for sliding raw data window                     |

| STARTAddWait            | The synchronous start pulse for address/raw length window                   |

| AddEnable               | The enable line for the address increment                                   |

| Address(9 to 0)         | The Address where the data has to be written in the packet                  |

| RawAdd                  | A line that indicates when the raw data has to be sent.                     |

| RawSlidingDone          | A pulse that indicates when the sliding raw data length is done             |

| ExtValidation           | A line that indicates when we are waiting for external validation           |

| MinDeadtimeDone         | Indicates that the minimum dead-time has been reached                       |

|                         |                                                                             |

| ComputedDone            | A synchronous pulse that indicates the end of the energy computation window |

|                         |                                                                             |

Table 24: WaitCounter I/Os

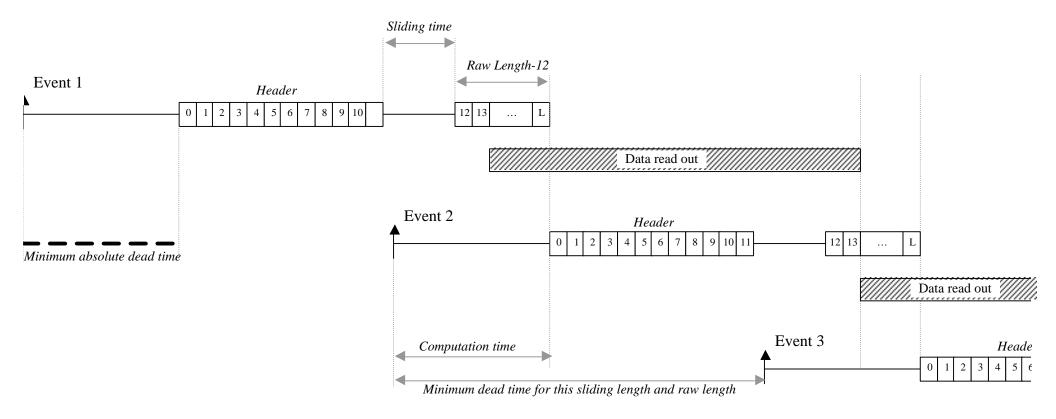

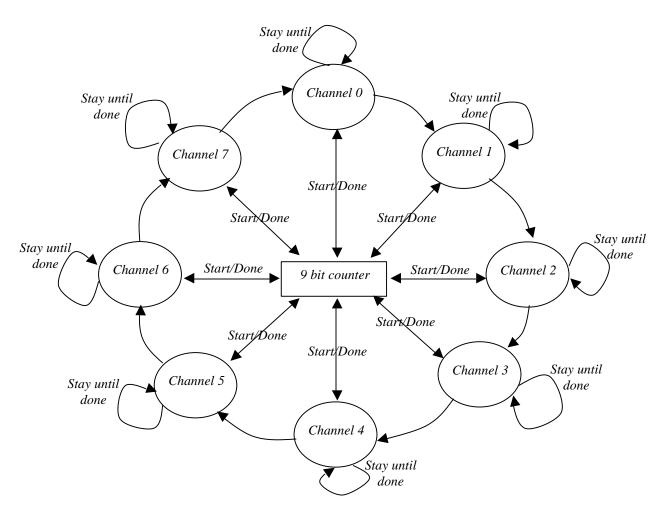

### XI.3 – StateMachine

This module implements the main channel housekeeping state-machines. It has two parallel state-machines

The system works around two state-machines in order to decrease the dead time. The time flow chart described in figure 16 (next page describe the use of resources and in particular the pre-buffer memory). Also is shown the time when the data can be read-out and sent to the outside world.

*Figure 16: Pre-buffer use by the state machine and the outside multiplexer*

The minimum dead-time for a given configuration can be computed as follows:

V2.5

Max(computation[internal trigger or external trigger], Raw length + sliding time) The dead-time is increased if the pre-buffer is not being emptied when a new event occurs.

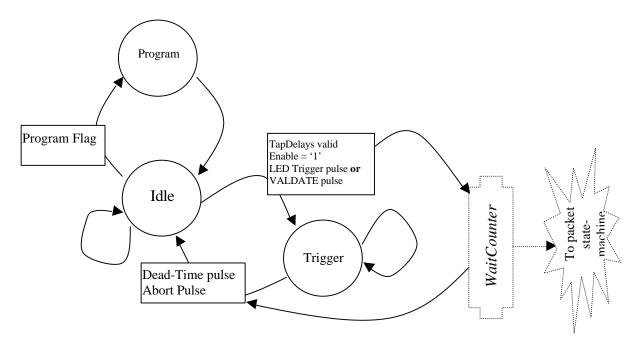

### XI.3.a – TimerMachine

One state machine is responsible for getting the timing and allowing for programming values. The other one is responsible for the packet creation and data retrieval.

Figure 17: timing/program state-machine

This state machine filters the various LED triggers or External triggers and when one trigger can be taken into account, it starts the dead time/processing timer. Any event arriving during this time will be discarded for packet creation.

| Signal Name            | Description                                    |

|------------------------|------------------------------------------------|

| RESET                  | Asynchronous reset. It is active high          |

| CLK                    | Clock.                                         |

| CHANNEL_ID             | The channel ID                                 |

| PROGData(15 to 0)      | The data retrieved by the VME module           |

| PROGAdd(5 to 0)        | The address retrieved by the VME module        |

| PROGFlag               | A flag indicating new data has been retrieved  |

| PROG_ACK               | A pulse acknowledging the programming          |

| TapDelay_Valid(4 to 0) | Status line from the tap delays                |

| LED_TIMESTAMP          | Timestamp pulse from the LED module            |

| VALIDATE               | A pulse indicating external trigger            |

| LED_SIGN               | Sign of the LED crossing                       |

| LATCH_TIMESTAMP        | A pulse getting the current timestamp          |

| LOADValidationWait     | The external validation length load pulse      |

| LOADPileupWait         | The pileup length load pulse                   |

| LOADExternalWait       | The external trigger sliding length load pulse |

| LOADm                  | The integration length load pulse              |

| Signal Name        | Description                                                    |

|--------------------|----------------------------------------------------------------|

| LOADk              | The collection length load pulse                               |

| LOADRawLength      | The raw data length load pulse                                 |

| LOADSlidingWait    | The raw data sliding length load pulse                         |

| LOAD_CFDa          | The CFD fraction load pulse                                    |

| LOAD_CFDTH         | The CFD Threshold load pulse                                   |

| LOAD_CFDTap        | The CFD delay length load pulse                                |

| LOAD_LEDTH         | The LED Threshold load pulse                                   |

| LOAD_LEDTimer      | The LED noise window length load pulse                         |

| StatusReg(15 to 0) | The status register that can be read back                      |

| STARTExternalWait  | The synchronous start pulse for external waiting window        |

| STARTInternalWait  | The synchronous start pulse for internal waiting window        |

| STARTValidation    | The synchronous start pulse for external validation window     |

| MinDeadtimeDone    | Indicates that the minimum dead-time has been reached          |

| Abort              | Indicates that the packet state-machine aborts (pileup or pre- |

|                    | buffer full)                                                   |

| CLEAR              | The clear line for the LED module                              |

Table 25: TimerMachine I/Os

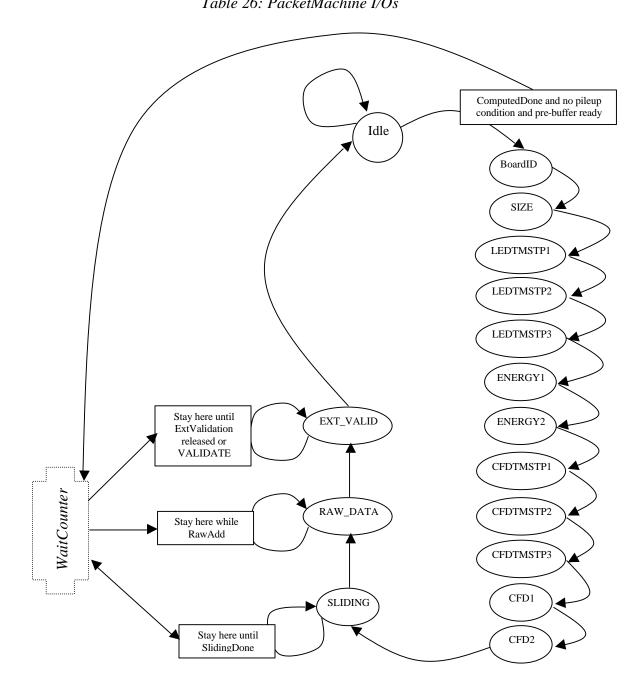

### XI.3.b – PacketMachine

This state machine is responsible for generating the cycles where we access the prebuffer.

| Signal Name       | Description                                                     |  |

|-------------------|-----------------------------------------------------------------|--|

| RESET             | Asynchronous reset. It is active high                           |  |

| CLK               | Clock.                                                          |  |

| TRIG_MODE(1 to 0) | Trigger mode as defined in register (table 21)                  |  |

| ENABLE            | START/STOP mode as defined in register (table 21)               |  |

| PILEUP            | PILEUP mode as defined in register (table 21)                   |  |

| EVENT_PILEUP      | Pileup flag on the current event                                |  |

| PREBUFFER_ACK     | Acknowledge from the VME interface module that the pre-         |  |

|                   | buffer is being read enough so that it can start being reused   |  |

| RawSlidingDone    | A pulse that indicates when the sliding raw data length is done |  |

| ExtValidation     | A line that indicates when we are waiting for external          |  |

|                   | validation                                                      |  |

| ComputedDone      | A synchronous pulse that indicates the end of the energy        |  |

|                   | computation window                                              |  |

| AddEnable         | The enable line for the address increment                       |  |

| RawAdd            | A line that indicates when the raw data has to be sent.         |  |

| VALIDATE          | A pulse indicating external validation                          |  |

| LATCH_TIMESTAMP   | A pulse getting the current timestamp                           |  |

| STARTSlidingWait  | The synchronous start pulse for sliding raw data window         |  |

| STARTAddWait      | The synchronous start pulse for address/raw length window       |  |

| PREBUFFER_READY   | A line indicating that the pre-buffer has been filled enough so |  |

|                   | that it can start being read on the VME side.                   |  |

| MUX_SELECT        | The selection bus                                               |  |

| e-buffer data enable line                                                                   |

|---------------------------------------------------------------------------------------------|

|                                                                                             |

| Il the data from the current event can be                                                   |

| or pileup prevents the data from being sent<br>and therefore we can rearm the event filter. |

|                                                                                             |

Figure 18: Packet State-machine

29

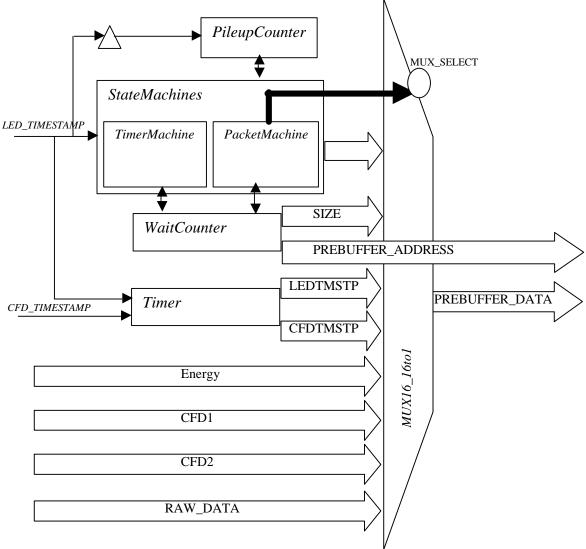

### XI.4 – PileupCounter

This module implements the pileup detection. It detects the following configurations:

- $\circ\,$  An event occurred less than the pileup length before when STARTEvent is launched.

- An event occurs less than the pileup length after the STARTEvent is lauched. (obviously a pileup length cannot be more than the minimum time between two STARTEvent)

- If two non considered events pileup but after the pileup length and before a new STARTEvent, the flag is not set.

The following timing diagrams show the various configuration and behaviors:

| Pileup<br>Windows | <u></u>                    |

|-------------------|----------------------------|

| LED               |                            |

| Filtered<br>LED   |                            |

| Pileup<br>Flag —— |                            |

|                   | Figure 19: Pre-pileup case |

| Pileup<br>Windows | <u>&lt;</u>                |

| LED               |                            |

| Filtered<br>LED   |                            |

| Pileup<br>Flag    |                            |

Figure 20: Post-pileup case one

30

| Pileup<br>Windows |          |

|-------------------|----------|

|                   | <u> </u> |

| LED               |          |

| Filtered<br>LED   |          |

| Pileup<br>Flag —— |          |

| Signal Name    | Description                                                       |

|----------------|-------------------------------------------------------------------|

| RESET          | Asynchronous reset. It is active high                             |

| CLK            | Clock.                                                            |

| LOADPileupWait | The pileup length load pulse                                      |

| PileupWait     | The pileup length                                                 |

| STARTPileup    | Any trigger from LED regardless of event filtering                |

| STARTEvent     | The trigger pulse for the event we consider                       |

| PILEUP_EVENT   | Line indicating if the current event being processed has a pileup |

|                | condition. (It is reset each time a new STARTEvent is sent).      |

Table 27: PileupCounter I/Os

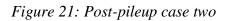

#### XI.5 – ProcCore

This module combines all the previous ones and implements the core processing and packet generation. It operates around 129MHz.

| Signal Name            | Description                                   |

|------------------------|-----------------------------------------------|

| RESET                  | Asynchronous reset. It is active high         |

| CLK                    | Clock.                                        |

| SYNCH                  | The timer synchronization pulse               |

| BOARD_ID (15 to 3)     | The Board ID                                  |

| CHANNEL_ID (2 to 0)    | The channel ID                                |

| PROGData(15 to 0)      | The data retrieved by the VME module          |

| PROGAdd(5 to 0)        | The address retrieved by the VME module       |

| PROGFlag               | A flag indicating new data has been retrieved |

| PROG_ACK               | A pulse acknowledging the programming         |

| TapDelay_Valid(4 to 0) | Status line from the tap delays               |

| RAW_DATA:(15 to 0)     | The Raw data from the last Tapdelay           |

| ENERGY (22 to 0)       | The energy from the peak detector             |

| Signal Name               | Description                                           |

|---------------------------|-------------------------------------------------------|

| CFD1 (15 to 0)            | CFD Y point 1                                         |

| CFD2 (15 to 0)            | CFD Y point 2                                         |

| CFD_TIMESTAMP             | The timestamp pulse for CFD                           |

| CFD_VALID                 | The flag indicating the CFD point are valid or not    |

| LED_TIMESTAMP             | Timestamp pulse from the LED module                   |

| LED_SIGN                  | Sign of the LED crossing                              |

| VALIDATE                  | Pulse validating an event in external validation      |

|                           | trigger mode                                          |

| LOADm                     | The integration length load pulse                     |

| LOADk                     | The collection length load pulse                      |

| LOAD_CFDa                 | The CFD fraction load pulse                           |

| LOAD_CFDTH                | The CFD Threshold load pulse                          |

| LOAD_CFDTap               | The CFD delay length load pulse                       |

| LOAD_LEDTH                | The LED Threshold load pulse                          |

| LOAD_LEDTimer             | The LED noise window length load pulse                |

| StatusReg(15 to 0)        | The status register that can be read back             |

| RESETEvent                | A pulse indicating all the data from the current      |

|                           | event can be discarded.                               |

| SIGNEvent                 | A line indicating the sign of the event that has been |

|                           | filtered by the states-machines. (When a              |

|                           | LATCH_TIMESTAMP is initiated).                        |

| PREBUFFER_ACK             | Acknowledge from the VME interface module that        |

|                           | the pre-buffer is being read enough so that it can    |

|                           | start being reused                                    |

| PREBUFFER_READY           | A line indicating that the pre-buffer has been filled |

|                           | enough so that it can start being read on the VME     |

|                           | side.                                                 |

| PREBUFFER_ADDRESS(9 to 0) | The Address where the data has to be written in the   |

|                           | packet                                                |

| PREBUFFER_DATA(15 to 0)   | The data that has to be written in the packet         |

| Size (8 to 0)             | Size of the packet in long words                      |

| PREBUFFER_EN              | Enable for the packet memory                          |

| CLEAR                     | The clear line for the LED module                     |

Table 28: WaitCounter I/Os

The resources used are as follows: Slices: 371 Block RAM: 0

The following figure shows the general interconnect between the sub-modules.

Figure 22: ProcCore simple interconnect (not all control lines are drawn)

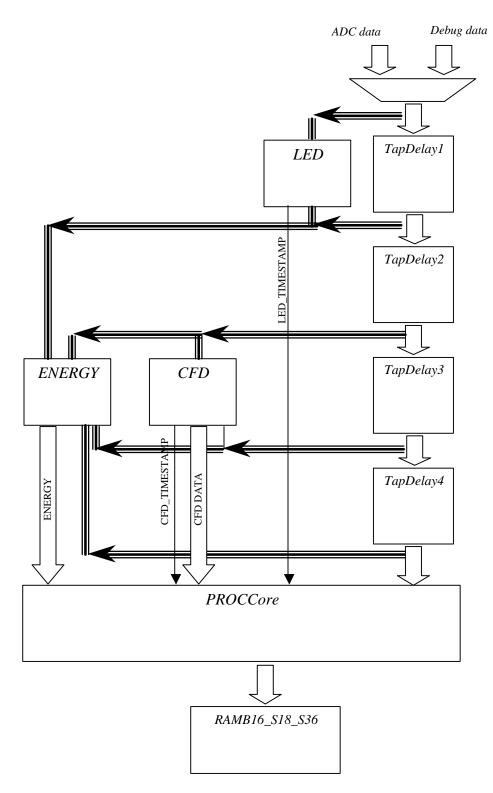

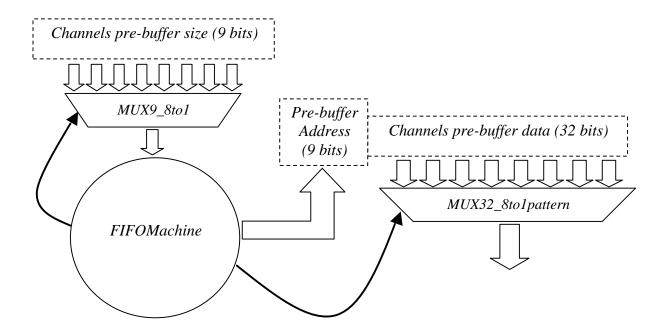

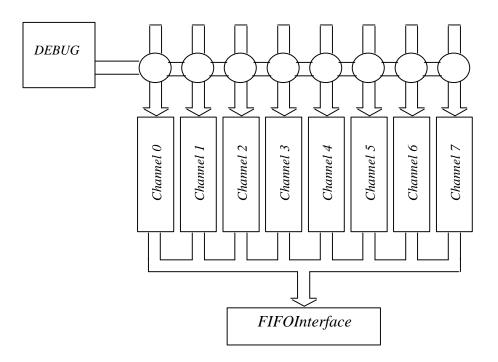

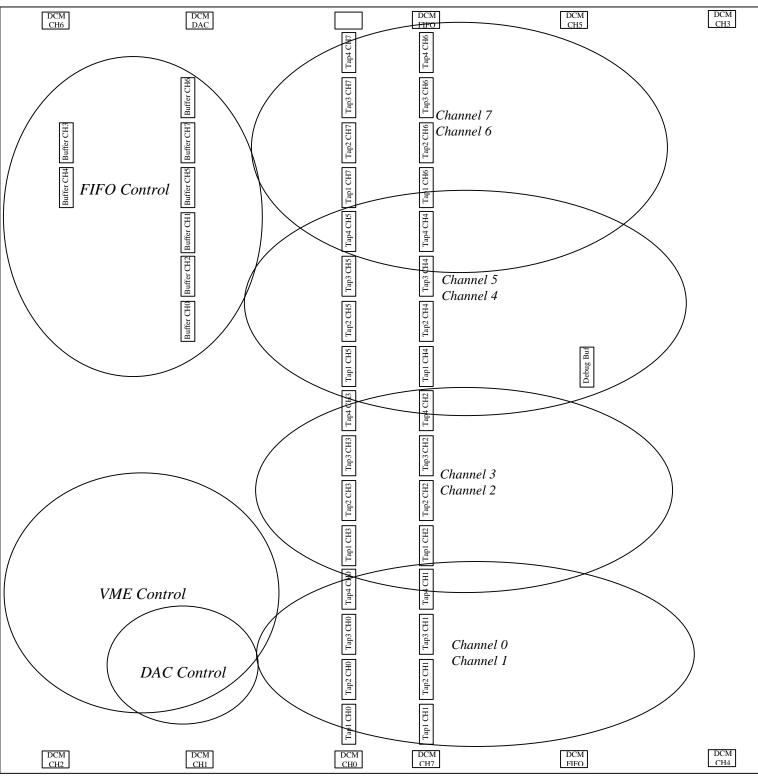

## XII – CHANNEL

This module implements the full digital processing for one channel. It includes the multiplexer for ADC data and debug data as well as the pre-buffer on the other end. It does not contains the VME load engine and the FIFO write engine as they are shared by all the channels.

The resources used are as follows: Slices: 925 Block RAM: 4

| Signal Name         | Description                                           |

|---------------------|-------------------------------------------------------|

| RESET               | Asynchronous reset. It is active high                 |

| CLK                 | Clock.                                                |

| SYNCH               | The timer synchronization pulse                       |

| BOARD_ID (15 to 3)  | The Board ID                                          |

| CHANNEL_ID (2 to 0) | The channel ID                                        |

| PROGData(15 to 0)   | The data retrieved by the VME module                  |

| PROGAdd(5 to 0)     | The address retrieved by the VME module               |

| PROGFlag            | A flag indicating new data has been retrieved         |

| PROG_ACK            | A pulse acknowledging the programming                 |

| ADCData(11 to 0)    | The Raw data from the ADC                             |