Revision n. 7 15 May 2009

> MOD. V862 series 32 CHANNEL INDIVIDUAL GATE QDCs

NPO:

00102/97:V862x.MUTx/07

CAEN will repair or replace any product within the guarantee period if the Guarantor declares that the product is defective due to workmanship or materials and has not been caused by mishandling, negligence on behalf of the User, accident or any abnormal conditions or operations.

CAEN declines all responsibility for damages or injuries caused by an improper use of the Modules due to negligence on behalf of the User. It is strongly recommended to read thoroughly the CAEN User's Manual before any kind of operation.

CAEN reserves the right to change partially or entirely the contents of this Manual at any time and without giving any notice.

## **Disposal of the Product**

The product must never be dumped in the Municipal Waste. Please check your local regulations for disposal of electronics products.

## TABLE OF CONTENTS

| 1. G | GENERAL DESCRIPTION                           |    |

|------|-----------------------------------------------|----|

| 1.1. | . Overview                                    |    |

| 1.2. |                                               |    |

|      |                                               |    |

| 2. P | PRINCIPLES OF OPERATION                       | 10 |

| 2.1. |                                               |    |

|      | 2.1.1. The input current-to-current converter |    |

| 2.2. |                                               |    |

|      |                                               |    |

| 2.3. |                                               |    |

| 2.4. |                                               |    |

| 2.5. | ` '                                           |    |

| 2.6. | EVENT COUNTER                                 | 17 |

| 2.7. | Busy Logic                                    | 18 |

| 2.8. | RESET LOGIC                                   | 18 |

| 2.9. | . FAST CLEAR                                  | 19 |

| 3. T | TECHNICAL SPECIFICATIONS                      | 20 |

| 3. 1 | TECHNICAL SPECIFICATIONS                      |    |

| 3.1. | . PACKAGING                                   | 20 |

| 3.2. | POWER REQUIREMENTS                            | 20 |

| 3.3. | FRONT PANEL                                   | 21 |

| 3.4. | EXTERNAL CONNECTORS                           | 22 |

|      | 3.4.1. INPUT connectors                       |    |

|      | 3.4.2. CONTROL connector                      |    |

| 3.5. |                                               |    |

|      | 3.5.1. Displays                               |    |

| 3.   | 3.5.2. Switches                               | 25 |

| 3.6. |                                               |    |

|      | 3.6.2. <i>Switches</i>                        |    |

|      | 3.6.3. Jumpers                                |    |

|      |                                               |    |

| 3.7. | . I ECHNICAL SPECIFICATIONS TABLE             | 29 |

| 4. V | VME INTERFACE                                 | 30 |

| 4.1. | . Addressing capability                       | 30 |

|      | 4.1.1. Addressing via Base Address            |    |

User's Manual (MUT)

| 4.1   | I.2. Addressing via GEOgraphical address                | 31 |

|-------|---------------------------------------------------------|----|

|       | 1.3. Base/GEO addressing examples                       |    |

|       | 1.4. MCST/CBLT addressing                               |    |

| 4.2.  | · ·                                                     |    |

|       | 2.1. Interrupt Status/ID                                |    |

|       | 2.2. Interrupt Level                                    | 35 |

|       | 2.3. Interrupt Generation2.4. Interrupt Request Release |    |

| 4.3.  | DATA TRANSFER CAPABILITY                                |    |

| 4.4.  | REGISTER ADDRESS MAP                                    |    |

| 4.5.  | MEMORY EVENT BUFFER (MEB)                               |    |

| 4.6.  | FIRMWARE REVISION REGISTER                              |    |

| 4.7.  | GEO Address Register                                    | 41 |

| 4.8.  | MCST/CBLT Address Register                              | 42 |

| 4.9.  | Bit Set 1 Register                                      | 42 |

| 4.10. | Bit Clear 1 Register                                    | 43 |

| 4.11. | Interrupt Level Register                                | 43 |

| 4.12. | INTERRUPT VECTOR REGISTER                               | 44 |

| 4.13. | Status Register 1                                       | 44 |

| 4.14. | CONTROL REGISTER 1                                      | 46 |

| 4.15. | Address Decoder High Register                           | 47 |

| 4.16. |                                                         |    |

| 4.17. |                                                         |    |

| 4.18. |                                                         |    |

| 4.19. | Event Trigger Register                                  | 48 |

| 4.20. | STATUS REGISTER 2                                       | 48 |

| 4.21. | EVENT COUNTER_LOW REGISTER                              | 49 |

| 4.22. |                                                         |    |

| 4.23. | INCREMENT EVENT REGISTER                                | 50 |

| 4.24. | INCREMENT OFFSET REGISTER                               | 50 |

| 4.25. | FAST CLEAR WINDOW REGISTER                              | 51 |

| 4.26. |                                                         |    |

| 4.27. |                                                         |    |

| 4.28. | , , , , , , , , , , , , , , , , , , ,                   |    |

| 4.29. | _                                                       |    |

| 4.30. | _                                                       |    |

| 4.31. | Crate Select Register                                   | 55 |

| 2. TEST EVENT WRITE REGISTER      | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3. EVENT COUNTER RESET REGISTER   | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4. IPED REGISTER                  | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5. R Memory Test Address Register | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6. SW COMM REGISTER               | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7. SLIDE CONSTANT REGISTER        | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8. AAD REGISTER                   | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9. BAD Register                   | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

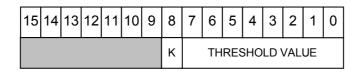

| O. Thresholds Memory              | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1. ROM memory                     | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OPERATING MODES                   | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SAFETY INFORMATION                | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Installation                      | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power ON sequence                 | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power ON STATUS                   | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OPERATION SEQUENCE                | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| REFERENCES                        | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ENDIX A                           | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

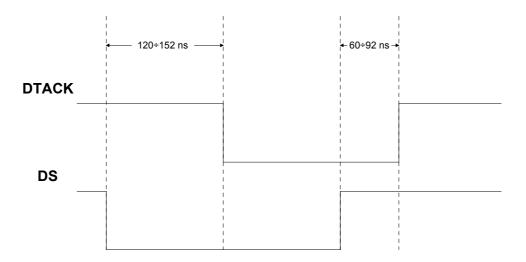

| F. INTERFACE TIMING               | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                   | 3. EVENT COUNTER RESET REGISTER  4. IPED REGISTER  5. R MEMORY TEST ADDRESS REGISTER  6. SW COMM REGISTER  7. SLIDE CONSTANT REGISTER  8. AAD REGISTER  9. BAD REGISTER  9. THRESHOLDS MEMORY  1. ROM MEMORY  1. ROM MEMORY  2. POPERATING MODES  SAFETY INFORMATION  INSTALLATION  POWER ON SEQUENCE  POWER ON STATUS  OPERATION SEQUENCE  TEST MODES  6.6.1. Random Memory Access Test Mode  6.6.2. Acquisition Test Mode  BLOCK TRANSFER MODE  ADVANCED SETTING AND READOUT MODES  8.8.1. Chained Block Transfer Mode  8.2. Multicast Commands  REFERENCES  NDIX A  EINTERFACE TIMING  VME CYCLE TIMING IN D16/D32 MODE  VME CYCLE TIMING IN D16/D32 MODE  VME CYCLE TIMING IN BLT / CBLT MODE |

## LIST OF FIGURES

| Fig. 1.1: Model type label (example V862 AC)                                          | 8  |

|---------------------------------------------------------------------------------------|----|

| Fig. 1.2: Model V862 Block Diagram                                                    | 9  |

| Fig. 2.1: Simplified block diagram of the QAC section                                 | 10 |

| Fig. 2.2: Signal conversion timing                                                    | 11 |

| Fig. 2.3: Input stage (simplified model)                                              | 12 |

| Fig. 2.4: IPED (μA) Vs IPED-Register setting                                          | 13 |

| Fig. 2.5: Block diagram of the sliding scale section                                  | 14 |

| Fig. 2.6: Zero suppression (Bit 8 of Bit Set 2 Register = 0, default setting)         | 15 |

| Fig. 2.7: Zero suppression (Bit 8 of Bit Set 2 Register =1)                           | 15 |

| Fig. 2.8: Multi-Event Buffer: Write pointer and Read pointer                          | 17 |

| Fig. 2.9: Fast Clear window                                                           | 19 |

| Fig. 3.1: Model V862 front panel                                                      | 21 |

| Fig. 3.2 INPUT connector (BLOCK A)                                                    | 22 |

| FIG. 3.3: CONTROL CONNECTOR PIN ASSIGNMENT                                            | 24 |

| FIG. 3.4: COMPONENT LOCATION (COMPONENT SIDE)                                         | 27 |

| Fig. 3.5: Components location (soldering side)                                        | 28 |

| Fig. 4.1: Binary-Hexadecimal representation of the board Address in GEO mode          | 31 |

| Fig. 4.2: Binary-Hexadecimal representation of Bit Set 1 Register Address in GEO mode | 31 |

| Fig. 4.3: Base/GEO Addressing: Example 1                                              | 32 |

| Fig. 4.4: MCST/CBLT Addressing Example                                                | 34 |

| Fig. 4.5: MEB: the Header                                                             | 38 |

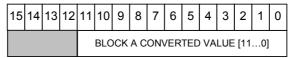

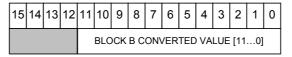

| Fig. 4.6: MEB: the data word format                                                   | 38 |

| FIG. 4.7: MEB: THE END OF BLOCK                                                       | 38 |

| Fig. 4.8: MEB: not valid datum                                                        | 40 |

| Fig. 4.9: Multi-Event Buffer: data structure example                                  | 40 |

| Fig. 4.10: Firmware Revision Register                                                 | 41 |

| Fig. 4.11: Geographical address register                                              | 41 |

| Fig. 4.12: MCST/CBLT address register                                                 | 42 |

| Fig. 4.13: Bit Set 1 Register                                                         | 43 |

| Fig. 4.14: Interrupt Level Register                                                   | 44 |

| Fig. 4.15: Interrupt Vector Register                                                  | 44 |

| Fig. 4.16: Status Register 1                                                          | 44 |

| Fig. 4.17: Control Register 1                                                         | 46 |

| Fig. 4.18: ADER HIGH Register                                                         | 47 |

User's Manual (MUT)

| Fig. 4.19: ADER LOW REGISTER                        | 47 |

|-----------------------------------------------------|----|

| Fig. 4.20: MCST Address Register                    | 47 |

| Fig. 4.21: Event Trigger Register                   | 48 |

| Fig. 4.22: Status Register 2                        | 49 |

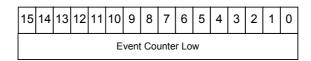

| Fig. 4.23: Event Counter Low Register               | 49 |

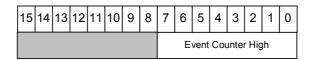

| Fig. 4.24: Event Counter High Register              | 50 |

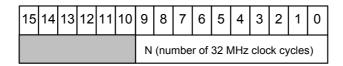

| Fig. 4.25: Fast Clear Window Register               | 51 |

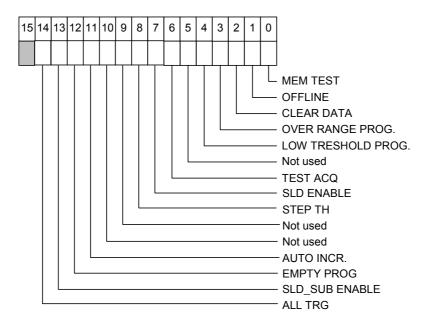

| Fig. 4.26: Bit set 2 register                       | 52 |

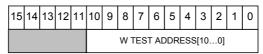

| Fig. 4.27: W Memory Test Address Register           | 54 |

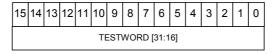

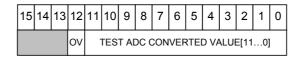

| Fig. 4.28: Test Word_High Register                  | 54 |

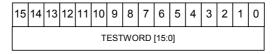

| Fig. 4.29: Test Word_Low Register                   | 54 |

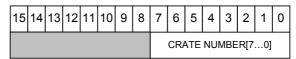

| Fig. 4.30: Crate Select Register                    | 55 |

| Fig. 4.31: Test Event Write Register                | 55 |

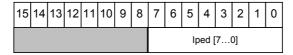

| Fig. 4.32: IPED REGISTER                            | 56 |

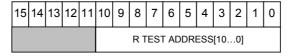

| Fig. 4.33: R Memory Test Address Register           | 56 |

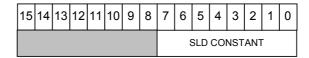

| Fig. 4.34: Slide Constant Register                  | 57 |

| Fig. 4.35: AAD Register                             | 57 |

| Fig. 4.36: BAD Register                             | 57 |

| Fig. 4.37: Threshold Register                       | 58 |

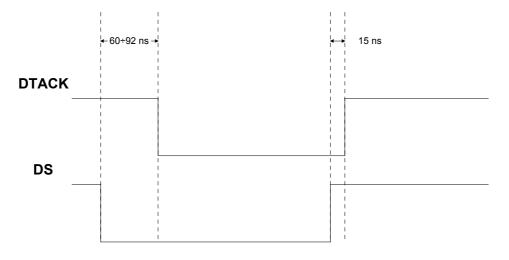

| Fig.A.1: VME cycle timing in D16 mode               | 68 |

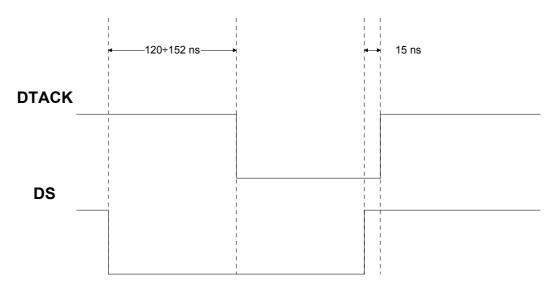

| Fig. A.2: VME cycle timing in BLT/CBLT mode         | 68 |

| FIG.A.3: VME CYCLE TIMING IN MBLT/CBLT64 MODE       | 69 |

| LIST OF TABLES                                      |    |

| TABLE 1.1: VERSIONS AVAILABLE FOR THE MODEL V862    | 8  |

| TABLE 2.1 – IPED VALUES                             | 13 |

| TABLE 3.1: MODEL V862 POWER REQUIREMENTS            | 20 |

| TABLE 3.2: MODEL V862 MAIN TECHNICAL SPECIFICATIONS | 29 |

| Table 4.1: Module recognised Address Modifier       | 30 |

## 1. General description

#### 1.1. Overview

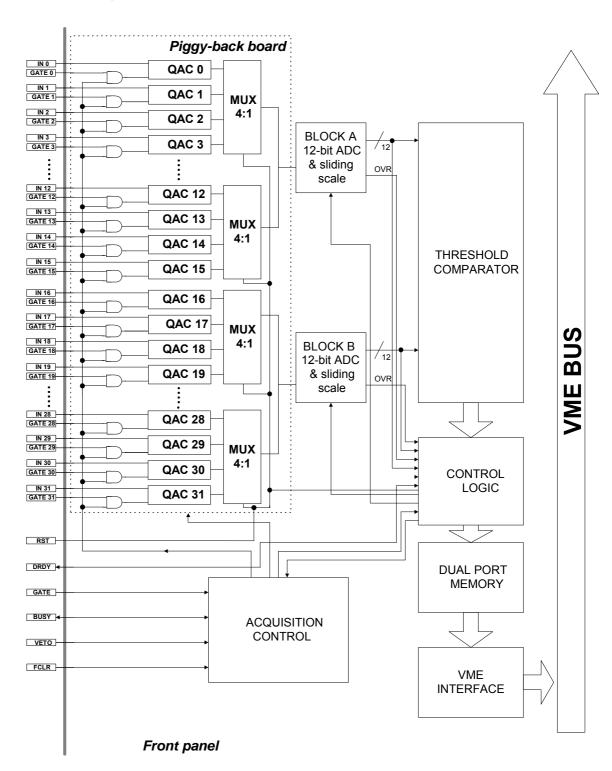

The Model V862 is a 1-unit wide VME 6U module housing 32 Charge-to-Digital Conversion channels with current integrating negative inputs (positive voltage inputs available on request). Each channel has an independent gate input (GATE i) in logical AND with a COMMON GATE input; the input charge on the i-th channel is converted to a voltage level by a QAC (Charge to Amplitude Conversion) section when both the GATE i and COMMON GATE signal are active. Input range is 0 ÷ 400 pC. The outputs of the QAC sections are multiplexed and subsequently converted by two fast 12-bit ADCs (5.7 µs for 32 channels). The ADCs use a sliding scale technique to reduce the differential non-linearity. The Mod. V862 offers a 32 event buffer memory; programmable zero suppression and trigger counter complete the features of the unit. The module works in A24/A32 mode. The data transfer occurs in D16, D32, BLT32, MBLT64 or CBLT32/CBLT64 mode. The unit also supports the Multicast commands.

The board is available both for standard and V430 VME crates and is equipped with a special circuitry (live insertion) that allows the User to insert it (or remove) into (or from) the crate without switching off.

Table 1.1: Versions available for the Model V862

| Version <sup>1</sup> | Number of channels | PAUX connector <sup>2</sup> | -5 V DC-DC converter |  |  |

|----------------------|--------------------|-----------------------------|----------------------|--|--|

| V862 AA <sup>3</sup> | 32                 | yes                         | no                   |  |  |

| V862 AC              | 32                 | no                          | yes                  |  |  |

Fig. 1.1: Model type label (example V862 AC)

<sup>&</sup>lt;sup>1</sup> A label on the printed board soldering side indicates the module's version (see Fig 1.1); all the versions share the same features except where indicated.

<sup>&</sup>lt;sup>2</sup> The version with the PAUX connector requires the V430 backplane.

<sup>&</sup>lt;sup>3</sup> Model available exclusively on request.

# 1.2. Block diagram

Fig. 1.2: Model V862 Block Diagram

## 2. Principles of operation

User's Manual (MUT)

The board has 32 channel inputs (ECL), 32 independent GATE i inputs (ECL) and one COMMON GATE input (ECL/NIM).

The integrated currents, received from the i-th channel input when both the GATE i and COMMON GATE signal are active, are converted into voltage levels by the QAC sections and then multiplexed and digitized by two fast 12-bit ADC modules.

Only the values that are above a programmable threshold (see § 2.3), do not cause overflow (see § 2.4) and are not killed (see § 2.3) will be stored in a dual port data memory accessible via VME.

In the following functional sections and operation principles of the module are described in some detail. The block diagram of the module can be found in Fig. 1.2.

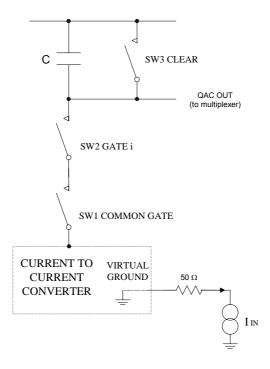

### 2.1. QAC sections

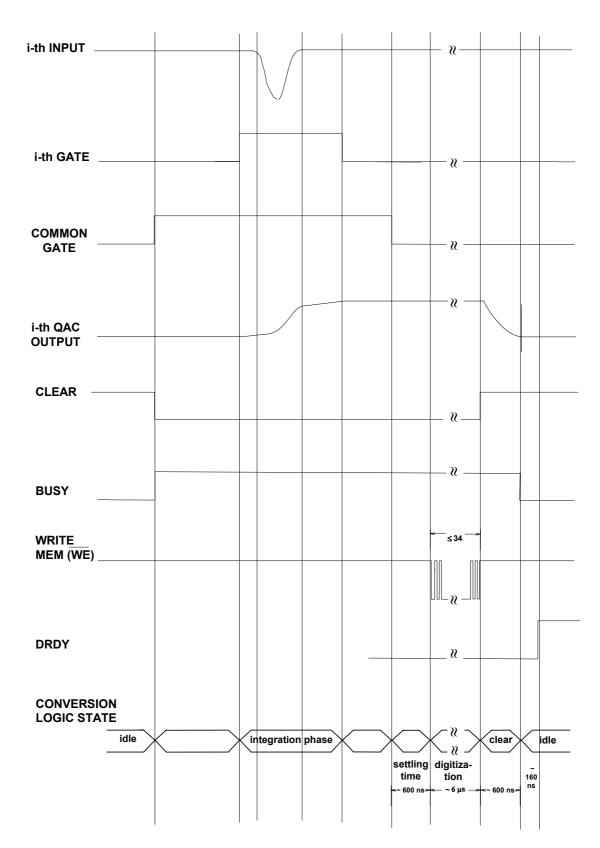

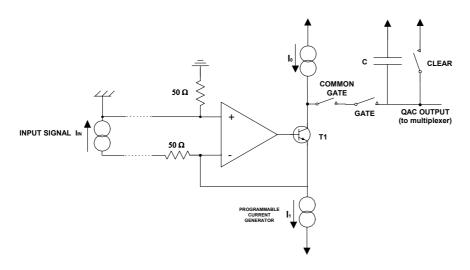

The module hosts 32 QAC sections: a simplified block diagram of a QAC section is reported in Fig. 2.1. The GATE i and the COMMON GATE signals close the switches SW1 and SW2 thus allowing the input current to flow through an integrator. The integrator output is amplified and fed to the multiplexer. As the SW1 and SW2 are open again, the signal is digitised by the 12-bit ADCs. After digitisation the SW3 switch is closed clearing the charge integrated into the capacitor C. The signal conversion timing is shown in Fig. 2.2.

Fig. 2.1: Simplified block diagram of the QAC section

**NPO:** 00102/97:V862x.MUTx/07

**Filename:** V862\_REV7.DOC

Number of pages:

Page:

10

Fig. 2.2: Signal conversion timing

#### 2.1.1. The input current-to-current converter

The input current to current converter (negative inputs) is shown in Fig. 2.3; it uses a differential amplifier and a bipolar transistor thus creating a virtual ground at the negative input terminal. A minimum bias current is required to flow through the transistor T1 in order to:

- Ensure T1 to operate in the linear region even for small input signals

- Linearly process small positive input currents

This bias current is provided by the  $I_0$  ( $\sim 500~\mu A$ ) and  $I_1$  (VME programmable) current generators (see figure below).

Fig. 2.3: Input stage (simplified model)

## 2.1.2. Pedestal

The QDC pedestal is the value readout when no input signal is present (open inputs). It is mainly due to the  $I_P$  current (see § 4.34) integrated by the capacitor C when a GATE signal is applied. It is worth noting that the QDC pedestal does not depend linearly on GATE width, as shown in § 2.1.2.1. When the maximum dynamic range is needed, it is possible to program  $I_1$  so that  $I_P$  is close to zero (see also § 4.34 for further details).

#### 2.1.2.1. Pedestal current setting

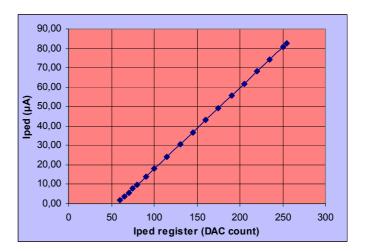

The following trace reports the graph of the Iped current (in  $\mu$ A) as a function of the IPED Register setting. This is obtained by using a gate of fixed width (100ns) and reading the digital ADC value, with the input signal disconnected; therefore only Iped is integrated. The integration capacitance is 100 pF, the QAC output is 1mV per count.

Table 2.1 shows that, below 55 DAC counts, the channel is "decoupled" and provides no output.

Our advice is not to set the Iped Register (see § 4.34) below 60 counts in order to guarantee the channels to be "coupled"; anyway if the User wishes to have the channels "coupled" precisely with the minimum possible Iped, then it is necessary to set the Iped Register between 50 and 60 DAC counts and to increase the gate in order to check that

the readout counts grows as the gate grows; if this does not happen, then Iped Register must be increased.

Table 2.1 – Iped values

| Dac   | Measure | Measure - offset gate | Iped       |

|-------|---------|-----------------------|------------|

| count | count   | count                 | (μΑ)       |

| 0     | 53,24   | - (*)                 | - (*)      |

| 10    | 53,21   | - (*)                 | - (*)      |

| 20    | 53,20   | - (*)                 | - (*)      |

| 30    | 53,21   | - (*)                 | - (*)      |

| 40    | 53,22   | - (*)                 | - (*)      |

| 50    | 53,19   | - (*)                 | - (*)      |

| 55    | 53,61   | t.b.d. (*)            | t.b.d. (*) |

| 60    | 55,13   | 1,94                  | 1,94       |

| 65    | 56,96   | 3,77                  | 3,77       |

| 70    | 58,98   | 5,79                  | 5,79       |

| 75    | 60,96   | 7,77                  | 7,77       |

| 80    | 63,03   | 9,84                  | 9,84       |

| 90    | 67,12   | 13,93                 | 13,93      |

| 100   | 71,23   | 18,04                 | 18,04      |

| 115   | 77,45   | 24,26                 | 24,26      |

| 130   | 83,77   | 30,58                 | 30,58      |

| 145   | 90,02   | 36,83                 | 36,83      |

| 160   | 96,26   | 43,07                 | 43,07      |

| 175   | 102,53  | 49,34                 | 49,34      |

| 190   | 108,79  | 55,60                 | 55,60      |

| 205   | 115,02  | 61,83                 | 61,83      |

| 220   | 121,25  | 68,06                 | 68,06      |

| 235   | 127,55  | 74,36                 | 74,36      |

| 250   | 133,77  | 80,58                 | 80,58      |

| 255   | 135,88  | 82,69                 | 82,69      |

Fig. 2.4: Iped  $(\mu A)$  Vs IPED-Register setting

#### 2.2. Analog to digital conversion

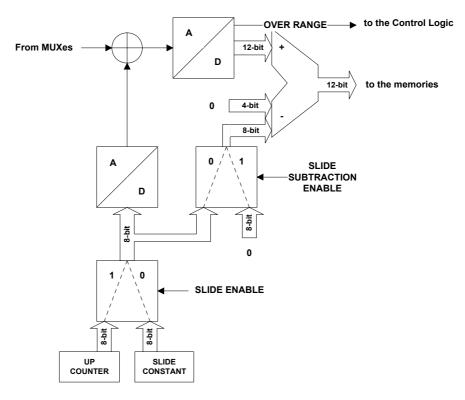

The output of each QAC section is multiplexed, by group of 4 channels, and subsequently converted by two fast 12-bit ADCs, each of which operates the conversion on a group of 16 channels (Block A and Block B ADCs). The ADC section supports the sliding scale technique to reduce the differential non-linearity (see references [1], [2]). This technique (see Fig. 2.5) consists in adding a known value to the analog level to be converted, thus spanning different ADC conversion regions with the same analog value. The known level is then digitally subtracted after the conversion and the final value is sent to the threshold comparator.

If the sliding scale is enabled, it reduces slightly the dynamic range of the ADC: the 12-bit digital output is valid from 0 to 3840, while the values from 3841 to 4095 are not correct.

Fig. 2.5: Block diagram of the sliding scale section

#### 2.3. **Zero suppression**

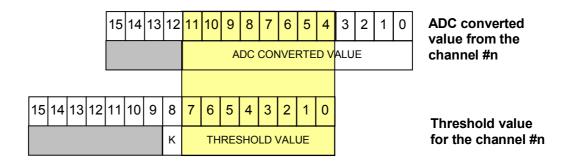

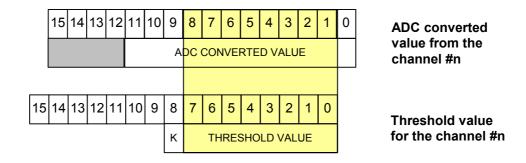

The output of the ADC is fed to a threshold comparator to perform the zero suppression. If the converted value from a channel is greater than (or equal to) the relevant low threshold value set via VME in the Thresholds memory (Base Address + 0x1080 ÷ 0x10BF, see § 4.40), the result is fed to the dual port memory and will be available for the readout.

If the converted value is lower than the threshold, the value is stored in the memory only if the LOW TRESHOLD PROG. bit of the Bit Set 2 Register is set to 1 (see § 4.26). The fact that the converted value was under the threshold is also flagged in the datum stored

NPO: Filename: Number of pages: Page: V862\_REV7.DOC 00102/97:V862x.MUTx/07 69 14

User's Manual (MUT)

in the memory, where the bit 13 (UNDERTHRESHOLD) of the 16-bit data word is set to 1 (see § 4.5).

The Thresholds memory allows to set a low threshold value for each channel. Default setting corresponds to thresholds not defined. By setting the bit 8 in the Bit Set 2 Register it is possible to program the Threshold values in 16 ADC counts steps over the entire full scale range or in 2 ADC counts steps over 1/8 of full scale range. In more detail, if Bit 8 = 0 (default value) the comparison is performed between the 8 MSB of each 12 bit converted value and the 8 bit threshold value which is stored in the relevant register as illustrated in Fig. 2.5. The threshold values can be programmed over the entire full scale range.

Fig. 2.6: Zero suppression (Bit 8 of Bit Set 2 Register = 0, default setting)

if Bit 8 = 1 (in the Bit Set 2 Register) the comparison is performed between the bit 1...8 of each 12 bit converted value and the 8 bit threshold value which is stored in the relevant register as illustrated in the figure below (converted value is under threshold if the value written in the 1...8 bits is smaller than the threshold value and 9...11 bits are 0). The threshold values can be programmed over 1/8 of full scale range.

Fig. 2.7: Zero suppression (Bit 8 of Bit Set 2 Register =1)

The comparison is resumed in the following table:

| Bit 8 of Bit Set 2 Register | Comparison                                 |

|-----------------------------|--------------------------------------------|

| 1                           | ADC CONVERTED VALUE < THRESHOLD VALUE x 2  |

| 0                           | ADC CONVERTED VALUE < THRESHOLD VALUE x 16 |

Page:

Title: Mod. V862, 32 channel Individual Gate ODC **Revision date:** 15/05/2009

Revision:

If the result of the comparison is true and the Bit 4 (LOW THRESHOLD PROG) of the Bit Set 2 Register is set to 0, data are skipped. If the Bit 4 of the Bit Set 2 Register is set to 1, the true result of the comparison is signaled by Bit 13 (UNDERTHRESHOLD) = 1 in the loaded data 16 bit word.

The content of the Threshold Register includes also a KILL bit, which allows to abort the memorisation of the datum even if it is higher than the threshold set in the register. This bit can thus be used to disable some channels. Refer to § 4.40 for further details.

The threshold values are lost only after switching the board off (a reset operation does not affect the threshold values).

## 2.4. Overflow suppression

The overflow suppression allows to abort the memorisation of data which originated an ADC overflow. The control logic provides to check if the output of the ADC is in overflow and, in the case, the value is not stored in the memory.

The overflow suppression can be disabled by means of the OVER RANGE PROG bit of the Bit Set 2 Register (see § 4.26): if this bit is set to 1, all the data, independently from the fact that they caused ADC overflow or not, are stored in the memory. In this case, the 16-bit word stored in the memory will have the bit 12 (OVERFLOW) set to 1 (see § 4.5).

## 2.5. Multiple Event Buffer (MEB)

After the conversion, if there is at least one converted value above the programmed threshold, not causing overflow and not killed, the control logic stores it in the Multi-Event Buffer (MEB).

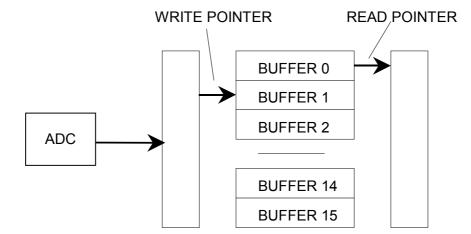

The Multi-Event Buffer is a Dual Port Memory (34 Words/event) which can store up to 32 events. It is mapped at the VME address: Base Address +  $0x0000 \div 0x07FC$  (see also § 4.5).

In order to trace the event flow, two pointers (Read and Write pointer) are employed. The Read Pointer points to the active read buffer.

The Write pointer is incremented automatically via hardware at the end of the channels conversion, while the Read pointer can be either incremented automatically (AUTO INCR. bit of the Bit Set 2 Register set to 1; see § 4.26) or via write access to one of two dummy registers, Increment Event and Increment Offset Registers (see § 4.23 and 4.24). These allow to move the readout pointer to the next event in the output buffer or to the next word, respectively. A read/write access to any location within the MEB memory segment results in a read/write operation at the location marked by the Read/Write pointer.

Fig. 2.8: Multi-Event Buffer: Write pointer and Read pointer

The MEB can be either in a "Full", a "Not empty" or an "Empty" status.

When the 5MSB of the Read pointer and the 5MSB of the Write pointer are different (i.e. point to different events), the MEB is in a "Not empty" status.

When the Read pointer and the Write pointer are equal, the MEB can be either in a "Full" or an "Empty" status. The MEB is full or empty according to the last increment pointer operation performed: if the last increment is the one of the Write pointer, the MEB is Full; if the last increment is the one of the Read pointer, the MEB is Empty.

The status of the MEB is monitored via two Registers, the Status Register 1 and the Status Register 2 (see § 4.13 and § 4.20, respectively).

After the conversion, the accepted data (i.e. the converted values above the programmed threshold, not causing overflow and not killed) are stored in the active event buffer (i.e. the one pointed by the write pointer) in subsequent 32-bit words. These are organised in events. Each event consists of a Header (see Fig. 4.5), a block

of data words (

Fig. 4.6) and an End-Of-Block (EOB) word (Fig. 4.7).

Each event contains thus from a minimum of 3 32-bit words (Header, one data word and EOB) to a maximum of 34 32-bit words (Header, 32 data words and EOB).

In case there are no accepted data, the User can choose to store anyway in the MEB the Header and the EOB relative to the event (see EMPTY PROG bit of the Bit Set 2 Register, see § 4.26): in this case the event is constituted by 2 32-bit words only.

#### 2.6. **Event Counter**

The module houses a 24-bit counter that counts the number of GATE signals that the module has received.

The Event Counter can work in two different modes, which can be selected via the Bit 14 (ALL TRG) of the Bit Set 2 Register (see § 4.26):

Mode A (ALL TRG = 1): it counts all events (default);

Mode B (ALL TRG = 0): it counts only the accepted events.

NPO: 00102/97:V862x.MUTx/07 Filename: V862\_REV7.DOC Number of pages: Page: 69

17

In the first case (Mode A), the Event Counter is increased each time a pulse is sent through the GATE input.

In the second case (Mode B), the Event Counter is increased each time a pulse, sent through the GATE input, is accepted (i.e. VETO, FCLR and BUSY are not active).

The value of the Event Counter is stored in the EOB of the Multi-Event Buffer (see § 4.5). The Event Counter is also stored in two registers, the Event Counter\_Low and Event Counter\_High Registers, which respectively contain the 16LSBs and the 8MSBs of the Event Counter (see § 4.21 and § 4.22).

## 2.7. Busy Logic

The board is BUSY either during the conversion sequence or during the reset of the analog section or when the MEB is not ready to accept data (MEB Full) or when the board is in Random Memory Access Test mode (see § 5.6.1).

On the occurrence of one of these conditions the front panel BUSY signal (CONTROL bus) is active, the red BUSY LED is on and the bit 2 (BUSY) and bit 3 (GLOBAL BUSY) of the Status Register 1 are set to 1 (see § 4.13).

The BUSY LED lights up also while the board is configuring (power ON).

Actually, each module sets to 1 its BUSY output after the leading edge of a pulse on the GATE input and releases it to 0 at the end of the conversion sequence. When the module is busy, it does not accept another GATE pulse.

The jumper J12 placed on the PCB (see Fig. 3.4) allows to select board behaviour in response to a BUSY status: if this jumper is set to EXTBSY, the acquisition is stopped as soon as any of the boards on the Control bus is BUSY; if the jumper is set to INTBSY, acquisition is stopped as the board is BUSY.

## 2.8. Reset Logic

Three different types of RESET operations can be distinguished, according to the effects they have on the module and particularly on the registers. These are:

- Type A: Data RESET

- Type B: Software RESET

- Type C: Hardware RESET

The **Data RESET** clears the data in the output buffer, resets the read and write pointers, the event counter and the QAC sections. It does not affect the registers.

This type of RESET can be forwarded in two ways:

- 1. setting the Bit 2 (CLEAR DATA) of the Bit Set 2 Register to 1 (see § 4.26); the Reset is released via the Bit Clear 2 Register (see § 4.27);

- 2. sending a RESET pulse from the front panel with the Bit 4 (PROG RESET) of the Control Register 1 set to 0 (see § 4.14).

Page:

18

Revi

The **Software RESET** performs the same actions as the data RESET and, moreover, it resets the registers marked in the column SR (Software Reset) in Table 4.2. This type of RESET can be forwarded in three ways:

- 1. setting the Bit 7 (SOFTWARE RESET) of the Bit Set 1 Register to 1 (see § 4.9): this sets the module to a permanent RESET status which is released only via write access, with the relevant bit set to 1, to the Bit Clear Register;

- 2. sending a RESET pulse from the front panel with the Bit 4 (PROG RESET) of the Control Register 1 set to 1 (see § 4.14);

- 3. performing a write access to the Single Shot Reset Register (see § 4.17): the RESET lasts as long as the write access itself.

The **Hardware RESET** performs the same actions as the Software RESET and, moreover, it resets further registers. All the registers reset by a Hardware RESET are marked in the column HR (Hardware Reset) in Table 4.2.

- This type of RESET is performed:

- 2. via a VME RESET (SYS RES).

1. at Power ON of the module;

At power ON or after a reset the module must thus be initialised.

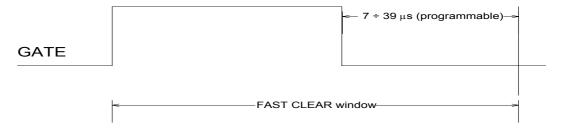

#### 2.9. FAST CLEAR

The FAST CLEAR of the module can be performed via the relevant front panel signal on the CONTROL connector (see § 3.4.2). A FAST CLEAR signal, generated at any time within the FAST CLEAR window, i.e. between the leading edge of the GATE signal and the end of the programmable time value set in the Fast Clear Window Register (see § 4.25), aborts the conversion. Its minimum width must be 30 ns.

N.B.: since a FAST CLEAR operation implies a CLEAR CONVERSION cycle, a new GATE signal is accepted only if it occurs at least 600 ns after the leading-edge of the FAST CLEAR signal.

Fig. 2.9: Fast Clear window

## 3.1. Packaging

User's Manual (MUT)

The Model V862 is housed in a 6U-high, 1U-wide VME unit. The board hosts the VME P1, P2 connectors and, depending on the version, the PAUX connector.

The version equipped with the PAUX connector (V862 AA) requires the VME V430 backplane.

## 3.2. Power requirements

The power requirements of the versions available for the V862 module are as follows:

Table 3.1: Model V862 power requirements

| Power supply | Mod.<br>V862 AA | Mod.<br>V862 AC |

|--------------|-----------------|-----------------|

| +12 V        | 1.1 A           | 1.1 A           |

| -12 V        | 350 mA          | 350 mA          |

| +5 V         | 1.8 A           | 3.9 A           |

| -5 V         | 1.5 A           | -               |

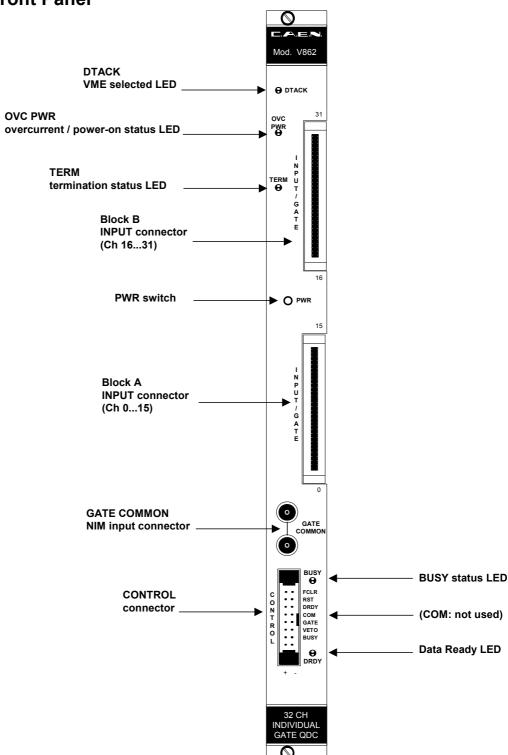

## 3.3. Front Panel

User's Manual (MUT)

Fig. 3.1: Model V862 front panel

3.4. External connectors

The location of the connectors is shown in Fig. 3.1. Their function and electro-mechanical specifications are listed in the following subsections.

## 3.4.1. INPUT connectors

Mechanical specifications:

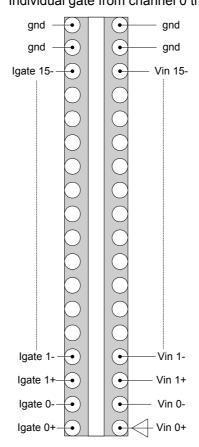

two 17+17-pin, RN P50E68P1SR1 type connectors (pin assignment shown in Fig. 3.2). *Electrical specifications:*

negative input signals (positive on request), 50  $\Omega$  impedance. Input range: 0 ÷ 400 pC. The 16<sup>th</sup> and 17<sup>th</sup> higher pair of pins of each connector is connected to ground.

**BLOCK A INPUT:** Input signals from channel 0 through channel 15

Individual gate from channel 0 through channel 15.

BLOCK B INPUT: Input signals from channel 16 through channel 31 Individual gate from channel 0 through channel 15

Fig. 3.2 INPUT connector (BLOCK A)

N.B.: individual gates must preceed input signals to be integrated of 15 ns at least.

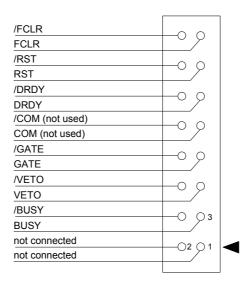

### 3.4.2. CONTROL connector

Mechanical specifications:

two 8+8-pin, 3M 3408-5202 Header-type connectors.

Pin assignment is shown in Fig. 3.3. The 1st lower pair of pins is not connected: they can be optionally connected to VEE (-5 V) or to DIGITAL GND by means of a soldering pad on the Printed Circuit Board. Refer to § 3.6.4 for further details.

All the control lines described below can be 110  $\Omega$  terminated on-board via internal DIP-switches, please refer to § 3.5.2 for further details

FCLR: Electrical specifications: diff. ECL input signal, active-high;

high impedance; min. width: 30 ns.

Function: FAST CLEAR signal, accepted if sent within the socalled FAST CLEAR window (see Fig. 2.8); it clears the QAC sections of the unit and aborts completely the conversion in

progress.

**RST:** Electrical specifications: diff. ECL input signal, active-high;

high impedance; min. width: 30 ns.

Function: clears the QAC sections, resets the Multi-Event Buffer status, stops pending ADCs conversions and, depending on the User's settings (see PROG RESET,

§ 4.14), may clear the control registers.

**DRDY:** Electrical specifications: diff. ECL input/output signal; high

impedance.

Function: indicates the presence of data in the output buffer of the board; DATA READY status is also flagged by the bit 0 of the Status Register 1; when several boards are daisy-chained, the wired OR and wired NAND of DATA READY signals can be read respectively on the DRDY+ and DRDY-lines of the CONTROL bus and the status of the DRDY+ bidirectional line is flagged by the bit 1 of the Status Register

1 (see § 4.13)

COM: (not used).

**GATE:** Electrical specifications: diff. ECL input signal, active-high;

high impedance.

Function: temporal window, common to all channels, within

which the individually gated inputs are accepted.

**VETO:** Electrical specifications: diff. ECL input signal, active-high;

high impedance.

Function: inhibits the conversion of the QAC signals.

**BUSY:** Electrical specifications: diff. ECL input/output signal; high

impedance.

Function: indicates that the board is either converting or resetting or in MEMORY TEST mode or the MEB is full, BUSY status is also flagged by the bit 2 of the Status Register 1; when several boards are daisy-chained, the wired OR and wired NAND of BUSY signals can be read respectively on the BUSY+ and BUSY- lines of the CONTROL bus and the status of the BUSY+ bidirectional line is flagged by the bit 3 of the

Status Register 1 (see § 4.13)

Fig. 3.3: CONTROL connector pin assignment

#### 3.4.3. GATE COMMON connectors

Mechanical specifications:

two bridged 00-type LEMO connectors.

Electrical specifications:

NIM std. input signals; high impedance; min. width: 10 ns. If this input is used a 50  $\Omega$  termination is required; in daisy-chain configuration, the termination must be inserted on the last board of the chain.

**GATE/COMMON:** Function: input signal, common to all channels, acting as the

temporal window within which the individually gated inputs are integrated. This signal is internally OR-wired with the GATE of

the CONTROL connector.

## 3.5. Other front panel components

#### 3.5.1. Displays

The front panel (refer to Fig. 3.1) hosts the following LEDs:

**DTACK:** *Colour:* green.

Function: DATA ACKNOWLEDGE command; it lights up each

time a VME access is performed.

Mod. V862, 32 channel Individual Gate ODC

Revision date: 15/05/2009

**Revision:**

**BUSY:** Colour: red.

> Function: it lights up each time the module is performing a conversion or resetting the analog section or in memory TEST mode or when the Multi-Event Buffer is full; it also lights up for a while at power ON to indicate that the board is configuring.

DRDY: Colour: yellow.

> Function: it lights up when at least one event is present in the output buffer; it also lights up for a while at power ON to

indicate that the board is configuring.

TERM: Colour: orange/green/red.

> Function: it lights up green when all the lines of the control bus are terminated, red when no line of the control bus is terminated. If only some lines are terminated, it is off. It also lights up orange for a while at power ON to indicate that the

board is configuring.

OVC/PWR: Colour: green/orange.

> Function: it lights up green when the board is inserted into the crate and the crate is powered up; when it is orange, it indicates that there is an over-current status: in this case, remove the overload source, switch the module off and then

switch it on again.

#### 3.5.2. Switches

PWR: *Type:* miniature flush plunger push-button switch.

> Function: after the insertion of the board into the crate, it allows to turn the board ON/OFF by pushing it with a pin.

Refer to § 5.3 for the power ON procedure

## 3.6. Internal hardware components

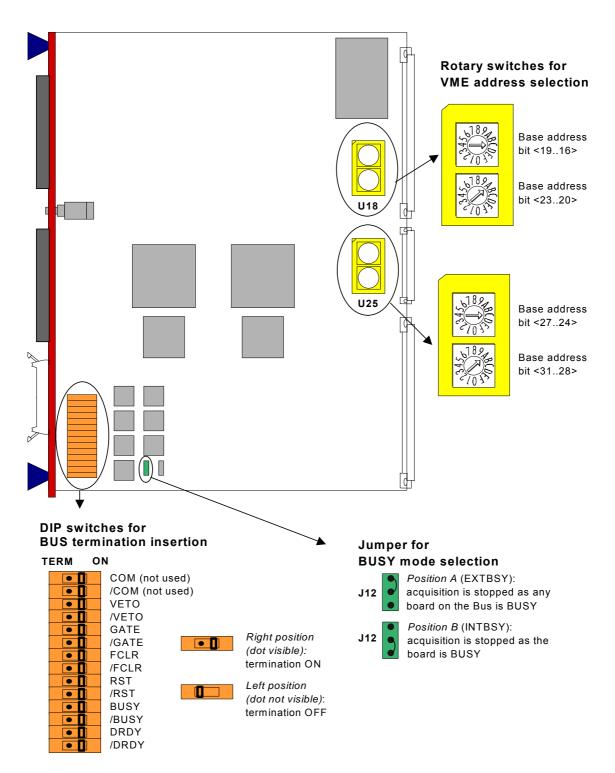

The V862 module is constituted by a motherboard with a piggy-back board plugged into it (see also Fig. 1.2 where the functional blocks hosted on the piggy-back board are pointed out). In the following some hardware setting components, located on the boards, are listed. Refer to Fig. 3.4 and Fig. 3.5 for their exact location on the PCB and their settings.

#### 3.6.2. Switches

**ROTARY SWITCHES:** *Type:* 4 rotary switches.

Function: they allow to select the VME address of the

module. Please refer to Fig. 3.4 for their settings.

**TERM ON:** Type: 14 DIP switches, a couple (positive and negative) for

each control signal.

Title:

Mod. V862, 32 channel Individual Gate ODC

**Revision date:** 15/05/2009

Revision:

Function: they allow the insertion of the Bus termination on the relevant line. The 110  $\Omega$ -termination must be inserted on the lines of the last board of the chain. In order to insert the termination on a given line, both the positive and the negative DIP switches must be set (refer to Fig. 3.4).

**Right position** (dot visible): the termination is inserted on the relevant line;

**Left position** (dot not visible): the termination is not inserted.

### 3.6.3. Jumpers

J12:

*Function:* it allows to select board behaviour in response to a BUSY status:

**Position A** (high): data acquisition is stopped as soon as any of the boards on the CONTROL Bus is BUSY;

**Position B** (low): data acquisition is stopped as the board is BUSY, independently from the status of the other boards on the CONTROL Bus.

Refer to Fig. 3.4 for the exact location of the jumper on the PCB and its setting.

Fig. 3.4: Component Location (component side)

Page:

27

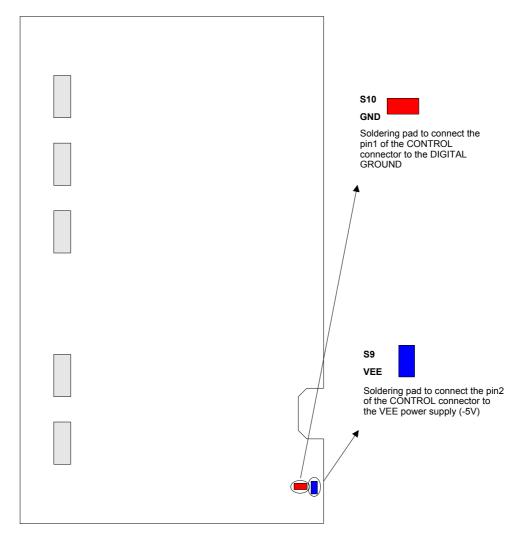

## 3.6.4. Soldering pads

S9 (VEE): Function: it allows to connect the second pin of the

CONTROL connector to the VEE power supply (-5 V).

No Soldering (default): the pin 2 of the CONTROL

connector is not connected.

Soldering: the pin 2 of the CONTROL connector is

connected to VEE power supply (-5 V).

**S10 (GND):** Function: it allows to connect the first pin of the CONTROL

connector to the DIGITAL GROUND.

No Soldering (default): the pin 1 of the CONTROL

connector is not connected.

Soldering: the pin 1 of the CONTROL connector is

connected to the digital ground.

Refer to Fig. 3.5 for the exact location of these pads on the PCB and their settings.

Fig. 3.5: Components location (soldering side)

**NPO:** 00102/97:V862x.MUTx/07

Filename: V862\_REV7.DOC

Number of pages: 69

Page: 28

# 3.7. Technical specifications table\*

User's Manual (MUT)

Table 3.2: Model V862 main technical specifications

| Packaging                    | 6U-high, 1U-wide VME unit (version AA requires the V430 backplane)                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Power requirements           | Refer to Table 3.1                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Input signals                | 32 channels, 50 $\Omega$ impedance, negative polarity, DC coupling                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Individual gate              | 32 differential ECL signals                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Input range                  | 0 ÷ 400 pC                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Resolution                   | 12 bit                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Gain                         | 100 fC/count                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| RMS Noise                    | 0.5 counts typical                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Integral non linearity       | ± 0.1% of Full Scale Range <sup>**</sup>                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Interchannel gain uniformity | ± 4%                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Interchannel Isolation       | > 60 dB                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Power rejection              | 0.002 count/mV (+5V); 0.01 count/mV (-5V)                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 1 Ower rejection             | 0.0046 count/mV (+12V); 0.0012 count/mV (-12V)                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Fast clear time              | 600 ns                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Gate delay                   | 15 ns                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Conversion time              | 5.7 μs for all channels                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| GATE COMMON input            | NIM signal, high impedance                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Control inputs               | active-high, differential ECL input signals:  GATE: common enabling signal for current integration.  RST: resets QAC sections, MEB status and control registers.  VETO: inhibits the conversion of the QAC signals.  FCLR: FAST CLEAR of QAC sections.                                                                                                                                            |  |  |  |  |  |  |  |

| Control outputs              | differential ECL output signals: <b>BUSY:</b> indicates the presence of data <b>DRDY:</b> board full, resetting, converting or in MEMORY TEST mode                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Displays                     | DTACK: green LED; lights up at each VME access. BUSY: red LED; alight during conversion, reset or Memory Test mode or as the MEB is full. DRDY: yellow LED; alight as there is one event in the MEB. TERM: orange/green/red LED; alight according to line terminations status. OVC/PWR: green/orange LED; green at board insertion; if orange, it indicates that there is an over-current status. |  |  |  |  |  |  |  |

<sup>\*</sup> Specifications measured on Mod. V862 version AA, employing a VME crate WIENER UEV5020 with UEP5021 power supply

NPO:

00102/97:V862x.MUTx/07

**Filename:** V862\_REV7.DOC

Number of pages: 69

$<sup>^{\</sup>ast\ast}$  measured from 5% to 95% of Full Scale Range

## 4. VME interface

## 4.1. Addressing capability

The modules can be addressed in three different ways, specifically:

- 1. via Base Address;

- 2. via GEOgraphical address;

- 3. via Multicast/Chained Block Transfer addressing mode.

## 4.1.1. Addressing via Base Address

The module works in A24/A32 mode. This implies that the module's address must be specified in a word of 24 or 32 bit. The Address Modifier codes recognised by the module are summarised in Table 4.1.

Table 4.1: Module recognised Address Modifier

| A.M. | Description                                          |

|------|------------------------------------------------------|

| 0x3F | A24 supervisory block transfer (BLT)                 |

| 0x3D | A24 supervisory data access                          |

| 0x3C | A24 supervisory 64 bit block transfer (MBLT)         |

| 0x3B | A24 non privileged block transfer (BLT)              |

| 0x39 | A24 non privileged User data access                  |

| 0x38 | A24 non privileged 64 bit block transfer (MBLT)      |

| 0x2F | Configuration Rom/Control & Status Register (CR/CSR) |

| 0x0F | A32 supervisory block transfer (BLT)                 |

| 0x0D | A32 supervisory data access                          |

| 0x0C | A32 supervisory 64 bit block transfer (MBLT)         |

| 0x0B | A32 non privileged block transfer (BLT)              |

| 0x09 | A32 non privileged data access                       |

| 0x08 | A32 non privileged 64 bit block transfer (MBLT)      |

The Base Address can be selected in the range:

0x0000000  $\longleftrightarrow$  0xFF0000 A24 mode 0x000000000  $\longleftrightarrow$  0xFFFF0000 A32 mode

The Base Address of the module can be fixed in two ways:

- by four rotary switches;

- by writing the Base Address in the ADER\_HIGH and ADER\_LOW registers.

The 4 rotary switches for Base Address selection are housed on two piggy-back boards plugged into the main printed circuit board (see Fig. 3.4).

Revi

To use this addressing mode the bit 4 of the Bit Set 1 Register (see § 4.9) must be set to 0. This is also the default setting.

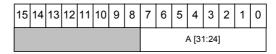

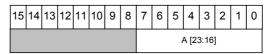

The module Base Address can be also fixed by using the Ader\_High and Ader\_Low Registers. These two registers set respectively the A[31:24] and the A[23:16] VME address bits (see § 4.15 and 4.16).

To use this addressing mode bit 4 of the Bit Set 1 Register (see § 4.9) must be set to 1.

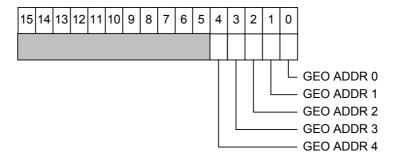

### 4.1.2. Addressing via GEOgraphical address

The module works in A24 mode only. The Address Modifiers codes recognised by the module are:

AM=0x2F: A24 GEO access

All registers except for the MEB (i.e. the CR/CSR area) can be accessed via geographical addressing.

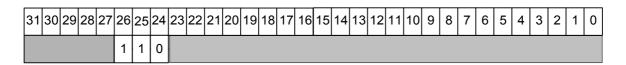

The geographical address is automatically read out at each RESET from the SN5..SN1 lines of the PAUX connector. Each slot of the VME crate is identified by the status of the SN5...SN1 lines: for example, the slot #5 will have these lines respectively at 00101 and consequently the module inserted in the slot #5 will have a GEO address set to 00101 (see Fig. 4.1).

The complete address in A24 mode for geographical addressing is:

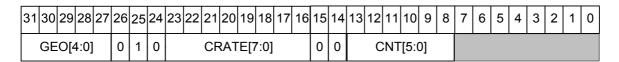

A[31:24] don't care A[23:19] GEO A[18:16] 0 A[15:0] offset

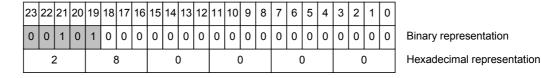

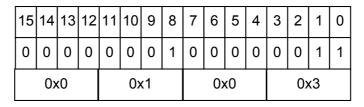

The following two figures show the binary and the hexadecimal representation of, respectively, the board Address and a Register Address (Bit Set 1 Register) in GEO addressing mode.

Fig. 4.1: Binary-Hexadecimal representation of the board Address in GEO mode

| 23 | 22               | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13                         | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |                       |

|----|------------------|----|----|----|----|----|----|----|----|----------------------------|----|----|----|---|---|---|---|---|---|---|---|---|---|-----------------------|

| 0  | 0                | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0                          | 1  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | Binary representation |

|    | 2 8 1006(offset) |    |    |    |    |    |    |    |    | Hexadecimal representation |    |    |    |   |   |   |   |   |   |   |   |   |   |                       |

Fig. 4.2: Binary-Hexadecimal representation of Bit Set 1 Register Address in GEO mode

**Revision date:** 15/05/2009

Revision:

N.B.: In the case of versions where the SN5...SN1 lines are not available (i.e. the versions without the PAUX connector), addressing via geographical address is not possible.

Although in these versions it is possible to perform a write access to the GEO Register (see § 4.6) for data identification during CBLT operation (see § 4.1.4), it is incorrect to use the GEO Register for addressing purposes when there is no PAUX.

### 4.1.3. Base/GEO addressing examples

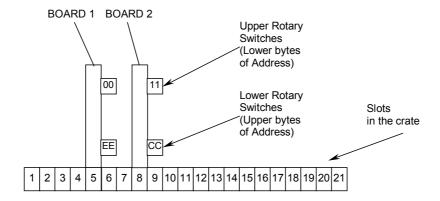

The following is an example of Base/GEO Addressing for two V862 boards inserted in a VME crate.

Fig. 4.3: Base/GEO Addressing: Example 1

If the board 1 and board 2 are respectively inserted in the slots 5 and 8 with the rotary switches for VME Base Addressing set as shown in the figure, the complete address of the registers of the two boards will be as follows:

Board 1:

Base addressing A32: 0xEE000000 + offset 0x000000 + offset

GEO addressing A24: 0x280000 + offset (MEB excluded).

Board 2:

Base addressing A32: 0xCC110000 + offset 0x110000 + offset

GEO addressing A24: 0x400000 + offset (MEB excluded).

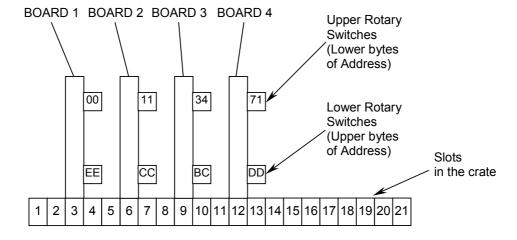

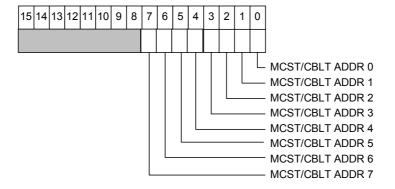

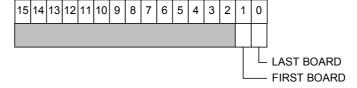

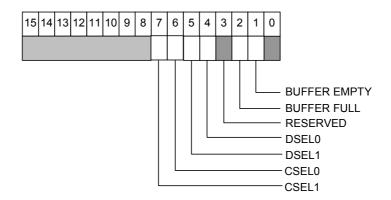

#### 4.1.4. MCST/CBLT addressing

When the Multicast/Chained Block Transfer addressing mode is adopted, the module works in A32 mode only. The Address Modifiers codes recognised by the module are:

AM=0x0F: A32 supervisory block transfer (CBLT)

AM=0x0D: A32 supervisory data access (MCST)

AM=0x0B: A32 User block transfer (CBLT)

AM=0x09: A32 User data access (MCST)

The boards can be accessed in Multicast Commands mode (MCST mode, see [4]), that allows to write in the registers of several boards at the same time by accessing the MCST Base Address in A32 only once.

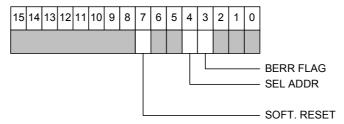

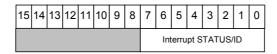

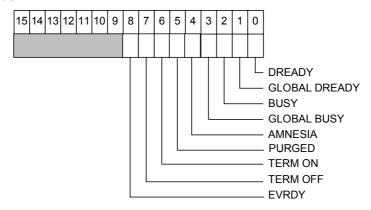

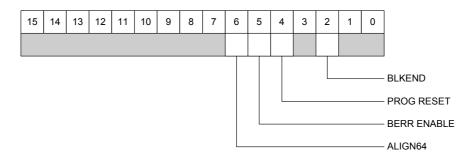

The boards can be accessed in Chained Block Transfer mode (CBLT mode, see [4]) that allows to readout sequentially a certain number of contiguous boards in a VME crate. This access is allowed in BLT32 and BLT64 modes only to the MCST Base Address.